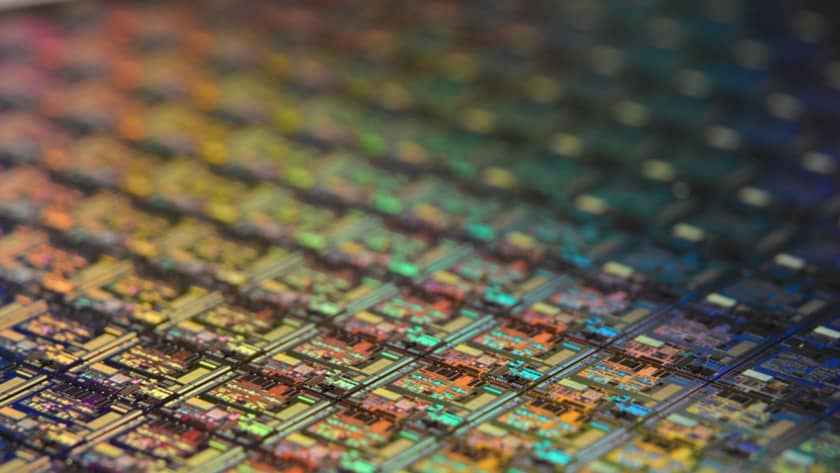

Dalla fine dello scorso anno, quando è iniziata la produzione in volumi di wafer con nodo di processo a 3 nm, la foundry taiwanese ha raggiunto il livello previsto di 100.000 wafer/mese da 12”, quasi tutti destinati ad Apple.

Anche se partita con sei mesi di ritardo rispetto a Samsung, TSMC ha surclassato in poco tempo la rivale sud-coreana raggiungendo una produzione di 100.000 wafer da 12” al mese col suo primo nodo di processo N3 a 3 nm al quale si sta affiancando il nodo N3E, più semplice e più economico. Attualmente il nodo N3 è in piena produzione con una resa che secondo indiscrezioni ha raggiunto l’incredibile valore dell’80%; l’attuale produzione è riservata esclusivamente ad Apple, l’unica in grado di sostenere i costi di questi wafer la cui quotazione unitaria è di circa 20.000 dollari.

Non bisogna essere dei geni in matematica per scoprire che solo da questa linea produttiva, TSMC incassa mensilmente circa 2 miliardi di dollari.

A conferma di questo semplice calcolo, il CEO di TSMC, CC Wei, ha recentemente dichiarato che il processo di produzione a 3 nm varrà più di 1,5 trilioni di dollari entro cinque anni dall’inizio della produzione in serie.

Attualmente, per il suo processo N3 TSMC utilizza la tecnologia FinFET, al contrario di Samsung che adotta già la tecnologia GAA (gate-all-around); TSMC passerà a questa tecnologia a partire dal processo a 2 nm in fase di implementazione nell’impianto di Zhuke. N3 è un processo particolarmente complesso e costoso, anche in termini energetici, che utilizza la litografia ultravioletta estrema (EUV) multi-pattern a 24 strati. L’evoluzione di questo processo è il nodo N3E che utilizza una tecnologia single-pattern a 19 strati, più semplice e più economica. I primi wafer N3E sono già in lavorazione e la produzione in volumi dovrebbe decollare nella seconda metà dell’anno. Questo nodo sarà utilizzato in progetti di altre aziende tra cui NVIDIA, AMD, Intel e Qualcomm.

TSMC ha aggiornato la sua roadmap tecnologica e commerciale durante il North America Technology Symposium che si è tenuto alla fine di aprile a Santa Clara, in California.

Durante l’edizione californiana del Symposium, è stata allestita anche un’Innovation Zone che ha accolto 18 start-up emergenti con i loro innovativi progetti.

“I nostri clienti non smettono mai di trovare nuovi modi per sfruttare la potenza del silicio per creare innovazioni che stupiranno il mondo e miglioreranno il nostro futuro“, ha affermato il Dr. CC Wei, CEO di TSMC. “Con lo stesso spirito, TSMC non si ferma mai e continuiamo a migliorare e far progredire le nostre tecnologie di processo con maggiori prestazioni, efficienza energetica e funzionalità in modo che la loro pipeline di innovazione possa continuare a fluire per molti anni a venire“.

Le tecnologie chiave evidenziate durante l’evento includono:

Più ampio portafoglio 3nm: N3P, N3X e N3AE – Con la tecnologia N3 già in produzione in volumi e con la versione N3E in pre-produzione, TSMC sta aggiungendo nuove varianti alla roadmap per soddisfare le diverse esigenze dei clienti.

- N3P, che dovrebbe entrare in produzione nella seconda metà del 2024, offre un ulteriore impulso a N3E con il 5% in più di velocità, una riduzione della potenza del 5-10% alla stessa velocità e una densità di chip 1,04 volte maggiore.

- N3X, che dà la priorità alle prestazioni e alle frequenze di clock per le applicazioni HPC, fornisce il 5% in più di velocità rispetto a N3P a una tensione di pilotaggio di 1,2 V, con la stessa densità di chip di N3P, e con la produzione in volumi prevista nel 2025.

- N3AE, o “Auto Early”, disponibile nel 2023, offre kit di progettazione di processi automobilistici (PDK) basati su N3E e consente ai clienti di lanciare progetti sul nodo 3nm per applicazioni automobilistiche, portando al processo N3A completamente qualificato per il settore automobilistico nel 2025.

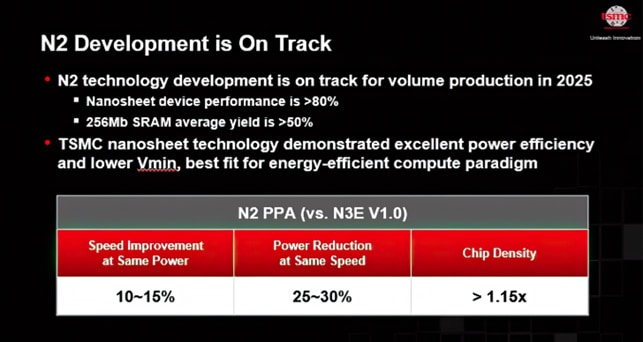

La tecnologia a 2 nm sta compiendo solidi progressi – Lo sviluppo della tecnologia a 2 nm di TSMC che impiega transistor nanosheet sta compiendo notevoli progressi sia in termini di rendimento che di prestazioni del dispositivo ed è sulla buona strada per la produzione nel 2025. Fornirà un miglioramento della velocità fino al 15% rispetto a N3E alla stessa potenza, e fino al 30% di riduzione della potenza alla stessa velocità e una densità del chip superiore a 1,15 volte.

Performance avanzate per la tecnologia CMOS RF con N4PRF. Oltre alla tecnologia N6RF annunciata nel 2021, TSMC sta sviluppando N4PRF, la tecnologia a radiofrequenza CMOS più avanzata del settore per applicazioni RF ad alta intensità digitale come WiFi 7 RF system-on-chip. N4PRF supporterà una densità logica 1,77 volte maggiore e il 45% in meno di potenza alla stessa velocità rispetto a N6RF.

TSMC 3DFabric Advanced Packaging e Silicon Stacking: i nuovi importanti sviluppi nelle tecnologie di integrazione del sistema 3DFabric di TSMC includono:

- Packaging avanzato – Per supportare le richieste delle applicazioni HPC di inserire più processori e memoria in un unico package, TSMC sta sviluppando una soluzione Chip on Wafer on Substrate (CoWoS) con un interposer RDL fino a 6 volte più grande (~5.000 mm2), in grado di di ospitare 12 stack di memoria HBM.

- 3D Chip Stacking – TSMC ha annunciato SoIC-P, versioni microbump delle sue soluzioni System on Integrated Chips (SoIC) che forniscono un modo conveniente per lo stacking di chip 3D. SoIC-P integra le soluzioni bumpless esistenti di TSMC per applicazioni di calcolo ad alte prestazioni (HPC), che ora sono conosciute come SoIC-X.

- Supporto alla progettazione – TSMC ha introdotto 3Dblox 1.5, la versione più recente del suo linguaggio di progettazione standard aperto per abbassare le barriere alla progettazione di circuiti integrati 3D. 3Dblox 1.5 aggiunge la sintesi automatizzata dei bump, aiutando i progettisti ad affrontare le complessità di die di grandi dimensioni con migliaia di bump e riducendo potenzialmente i tempi di progettazione di mesi.

Per quanto riguarda la tecnologia a 2 nm, già quest’anno saranno disponibili wafer di preproduzione destinati a Apple e NVIDIA, le uniche aziende con ordini in corso per questo nodo di processo. La produzione in volumi è prevista per gli inizi del 2025. Il prezzo indicativo dei wafer realizzati con questo nodo di processo sarà di circa 25.000 dollari.