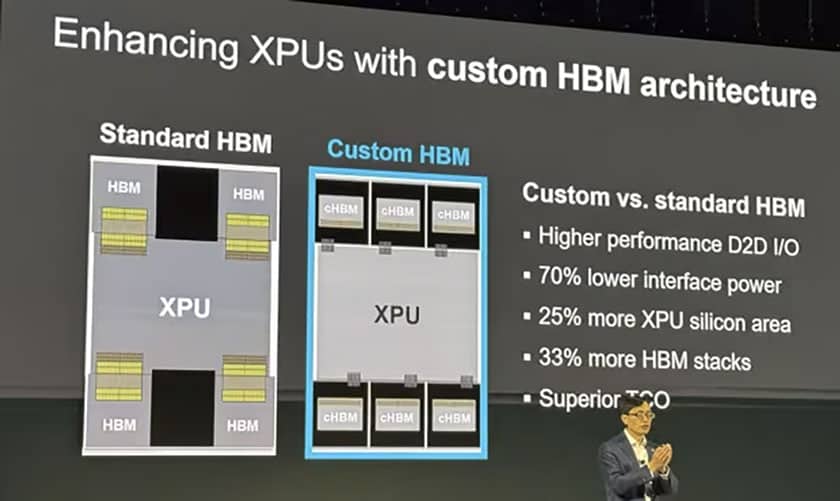

La nuova architettura dell’acceleratore Marvell AI (XPU) consente fino al 25% di capacità di elaborazione in più, il 33% di memoria in più e un miglioramento dell’efficienza energetica. L’architettura comprende interfacce die-to-die avanzate, die di base HBM, logica del controller e packaging avanzato per nuovi progetti XPU.

Marvell Technology ha annunciato di aver avviato una nuova architettura di elaborazione HBM personalizzata che consente alle XPU di ottenere una maggiore densità di elaborazione e memoria. La nuova tecnologia è disponibile per tutti i suoi clienti di silicio personalizzato per migliorare le prestazioni, l’efficienza e il TCO delle loro XPU personalizzate. Marvell sta collaborando con i suoi clienti cloud e i principali produttori di HBM, Micron, Samsung Electronics e SK hynix, per definire e sviluppare soluzioni HBM personalizzate per le XPU di prossima generazione.

HBM è un componente critico integrato all’interno dell’XPU che utilizza la tecnologia avanzata di packaging 2.5D e interfacce standard del settore ad alta velocità. Tuttavia, la scalabilità delle XPU è limitata dall’attuale architettura basata su interfaccia standard. La nuova architettura di elaborazione HBM personalizzata di Marvell introduce interfacce su misura per ottimizzare prestazioni, potenza, dimensioni del die e costi per progetti XPU specifici.

Questo approccio considera il silicio di elaborazione, gli stack HBM e il packaging. Personalizzando il sottosistema di memoria HBM, incluso lo stack stesso, Marvell sta promuovendo la personalizzazione nell’infrastruttura del data center cloud. Marvell sta collaborando con i principali produttori di HBM per implementare questa nuova architettura e soddisfare le esigenze degli operatori del data center cloud.

L’architettura di elaborazione HBM personalizzata di Marvell migliora le XPU serializzando e velocizzando le interfacce I/O tra i suoi die in silicio dell’acceleratore di elaborazione AI interno e i die di base HBM. Ciò si traduce in prestazioni maggiori e fino al 70% di potenza di interfaccia inferiore rispetto alle interfacce HBM standard. Le interfacce ottimizzate riducono anche lo spazio in silicio richiesto in ogni die, consentendo alla logica di supporto HBM di essere integrata nel die di base.

Questi risparmi di spazio, fino al 25%, possono essere utilizzati per migliorare le capacità di elaborazione, aggiungere nuove funzionalità e supportare fino al 33% in più di stack HBM, aumentando la capacità di memoria per XPU. Questi miglioramenti aumentano le prestazioni e l’efficienza energetica delle XPU, riducendo al contempo il TCO per gli operatori cloud.

I commenti

“I principali operatori di data center cloud hanno scalato con infrastrutture personalizzate. Il potenziamento delle XPU adattando HBM per prestazioni specifiche, potenza e costo totale di proprietà è l’ultimo passo in un nuovo paradigma nel modo in cui gli acceleratori AI sono progettati e forniti”, ha affermato Will Chu, Senior Vice President e General Manager del Custom, Compute and Storage Group presso Marvell. “Siamo molto grati di lavorare con i principali progettisti di memoria per accelerare questa rivoluzione e aiutare gli operatori di data center cloud a continuare a scalare le loro XPU e infrastrutture per l’era dell’AI“.

“Una maggiore capacità di memoria e larghezza di banda aiuteranno gli operatori cloud a scalare in modo efficiente la loro infrastruttura per l’era dell’intelligenza artificiale”, ha affermato Raj Narasimhan, vicepresidente senior e direttore generale della Compute and Networking Business Unit di Micron. “Le collaborazioni strategiche incentrate sull’efficienza energetica, come quella che abbiamo con Marvell, si baseranno sulle specifiche di potenza HBM leader del settore di Micron e forniranno agli hyperscaler una piattaforma solida per fornire le capacità e le prestazioni ottimali richieste per scalare l’intelligenza artificiale”.

“L’ottimizzazione di HBM per XPU e ambienti software specifici migliorerà notevolmente le prestazioni dell’infrastruttura degli operatori cloud e garantirà un uso efficiente dell’energia“, ha affermato Harry Yoon, vicepresidente esecutivo aziendale di Samsung Electronics e responsabile della pianificazione di prodotti e soluzioni per le Americhe. “Il progresso dell’IA dipende da tali sforzi mirati. Non vediamo l’ora di collaborare con Marvell, un leader nell’innovazione del silicio di elaborazione personalizzato”.

“Collaborando con Marvell, possiamo aiutare i nostri clienti a produrre una soluzione più ottimizzata per i loro carichi di lavoro e infrastrutture“, ha affermato Sunny Kang, VP di DRAM Technology, SK hynix America. “Come uno dei principali pionieri di HBM, non vediamo l’ora di dare forma a questa prossima fase evolutiva per la tecnologia”.