Lo scanner pilota Twinscan EXE:5000 con apertura numerica 0,55 verrà installato entro quest’anno presso l’”imec-ASML High NA Lab” di Leuven, in Belgio, per consentire ai principali produttori di chip di studiare e adattare le tecnologie di processo a questo nuovo strumento di produzione.

La conferma arriva dal CEO di ASML Peter Wennink che in una intervista alla Reuters ha dichiarato che lo scanner pilota EUV ad alto NA Twinscan EXE:5000 verrà consegnato entro la fine di quest’anno. “Alcuni fornitori hanno avuto qualche difficoltà nel raggiungere l’atteso livello di qualità tecnologica portando a qualche ritardo. Ma in realtà la prima spedizione è confermata per quest’anno.”

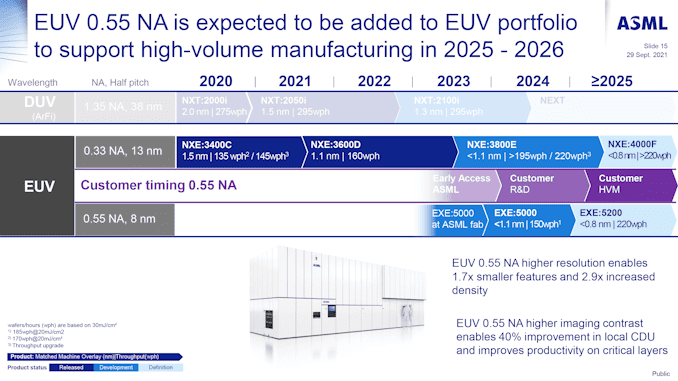

Questo primo prototipo consentirà ai produttori di chip all’avanguardia – TSMC, Intel, Samsung, SK Hynix e Micron – di adattare i processi produttivi alla tecnologia EUV High-NA, fornendo anche un importante feedback ad ASML per la produzione dello scanner EUV High-NA di livello commerciale Twinscan EXE:5200 che verrà consegnato ai clienti a partire dal 2025 e che consentirà di produrre chip logici con nodo di processo sub-2nm con pattern singoli.

Attualmente, gli scanner EUV più sofisticati sono il modello Twinscan NXE:3400D adatto per la produzione in volumi dei nodi logici da 5 e 3 nm con pattern singolo/doppio e il modello Twinscan NXE:3400C adatto per la produzione in volumi dei nodi logici da 7 e 5 nm con pattern singolo. Entrambi questi modelli sono dotati di ottica con apertura numerica (NA) da 0,33, che offre una risoluzione di 13 nm. Tale risoluzione è adatta per incidere chip con passi metallici compresi tra 30 nm e 38 nm. Tuttavia, quando i passi scendono al di sotto di 30 nm (per nodi sotto i 3 nm), la risoluzione di 13 nm non è più sufficiente e i produttori di chip devono fare ricorso a tecnologie EUV double patterning e/o pattern shaping. E come in tutti i processi multi-patterning, i costi aumentano e la resa diminuisce.

Per questo motivo, ASML ha messo in cantiere la piattaforma EUV di prossima generazione che aumenta l’apertura numerica (NA) da 0,33 a 0,55 (“High-NA”) per ottenere una risoluzione di 8 nm che consente di realizzare nodi logici a 2 nm con un singolo passaggio e, probabilmente, nodi ancora più avanzati con processi multi-patterning, oltre che nodi di memoria con densità simile.

Questa la roadmap di ASML per gli scanner con tecnologia EUV:

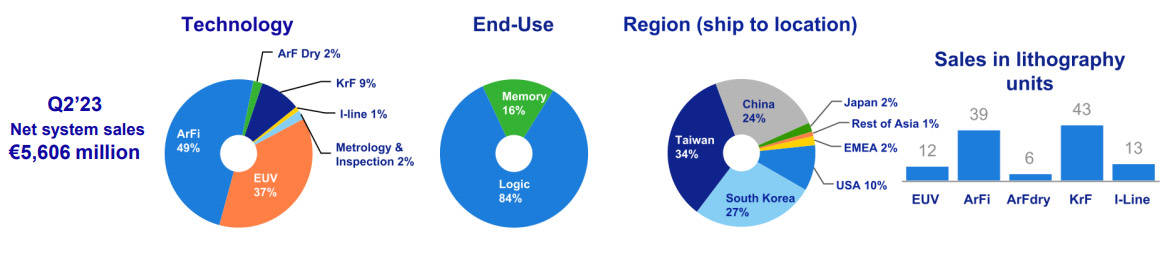

Attualmente le uniche aziende al mondo ad utilizzare gli scanner EUV di ASML sono TSMC, Samsung e Intel per quanto riguarda i nodi logici, mentre solo recentemente sono state adottate anche dai produttori di memorie SK Hynex e Micron (oltre che da Samsung).

Nessuna di queste macchine può essere venduta ai produttori cinesi di chip a causa delle restrizioni introdotte dagli Stati Uniti. Pur essendo prodotte nei Paesi Bassi, infatti, molti elementi utilizzano tecnologia americana o montano componenti provenienti dagli Stati Uniti; ad esempio, queste macchine montano una sorgente luminosa sviluppata a San Diego, in California mentre il reticolo è prodotto a Wilton, in Connecticut. A maggior ragione, anche gli scanner EUV High-NA di nuova generazione non potranno essere esportati in Cina.

Al momento solo TSMC e Samsung stanno producendo in volumi chip logici con nodo di processo avanzato (5, 4 e 3 nm) mentre SK Hynex ha rallentato la produzione di DRAM avanzate a causa della crisi del mercato delle memorie e Micron è ancora in fase di pre-produzione.

Per quanto riguarda Intel, l’azienda californiana sembra voler anticipare i tempi della produzione del processo più avanzato 18A (2 nm) al 2024 utilizzando la nuova macchina EUV (sempre a 0,33 NA) Twinscan NXE:3800E e facendo ricorso alla doppia esposizione; rispetto allo scanner NXE:3600D, il nuovo sistema presenta prestazioni leggermente superiori ed una capacità oraria superiore del 25% in termini di Wph (wafer per hour). Intel intende utilizzare anche il nuovo sistema di modellazione del pattern Centura Sculpta di Applied Materials per ridurre il numero di passaggi litografici EUV e ridurre gli errori di allineamento. Solo nel 2025, quando saranno disponibili, Intel passerà allo scanner EUV High-NA Twinscan EXE:5200.

Il costo del nuovo scanner EUV High-NA non è stato ancora definito ma sarà sicuramente superiore ai 300 milioni di dollari, contro i 200 milioni circa dei modelli EUV attualmente disponibili.

IL CEO di ASML ha anche confermato che le entrate generate dagli scanner DUV saranno superiori quest’anno a quelle dei sistemi EUV grazie ai numerosi ordini provenienti dalla Cina. Con i sistemi DUV più avanzati è possibile realizzare chip a 14 nm, valore che può scendere a 7 nm con processi multi-patterning, tecnologia utilizzata da SMIC per produrre per Huawei il nuovo Kirin 9000s di cui tanto si parla in questi giorni.

Il timore di ASML è che vengano introdotte nuove restrizioni alle esportazioni verso la Cina di sistemi DUV avanzati, dopo quelle entrate in vigore il 1° settembre di quest’anno. Come si vede nel riepilogo delle vendite del secondo trimestre di quest’anno, la Cina rappresenta per l’azienda olandese il 24% delle entrate.

Hyper NA EUV: le prossime macchine per litografia con apertura 0,75 in arrivo tra dieci anni

Recentemente, il Chief Business Officer (CBO) di ASML Christophe Fouquet ha sottolineato la necessità di sviluppare una tecnologia EUV di esposizione ultraelevata con apertura NA = 0,75 a partire dal 2030.

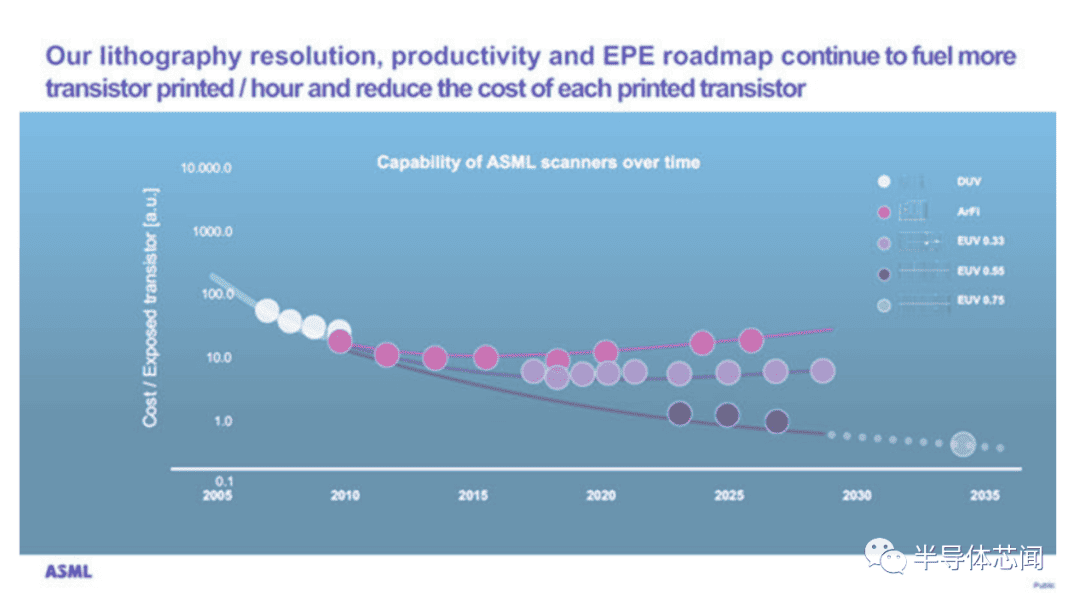

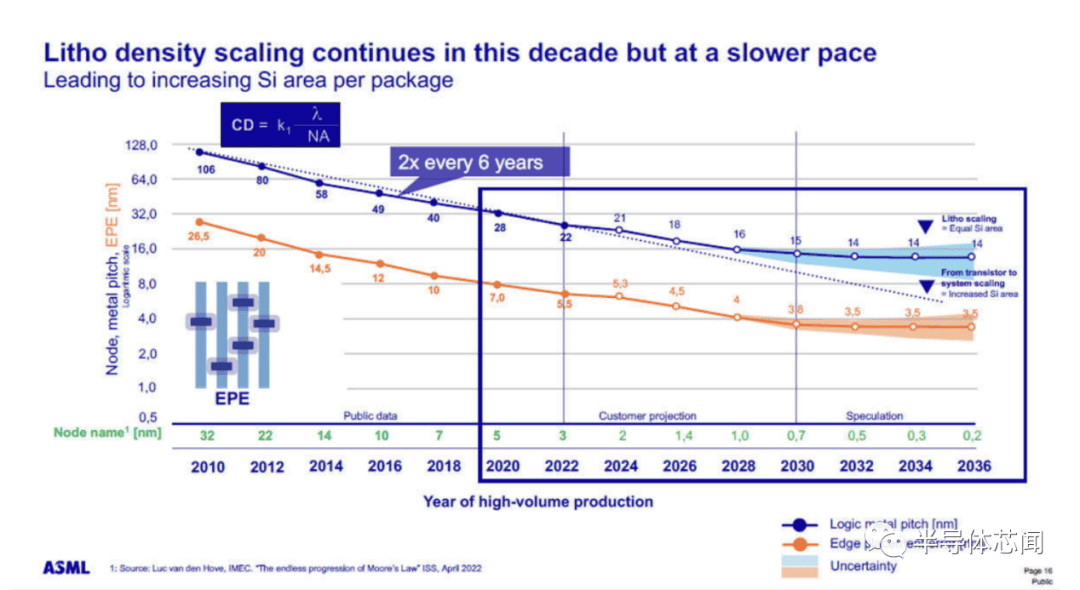

Fouquet ha descritto i cambiamenti registrati nei cablaggi metallici attraverso l’esposizione e l’EPE (Edge Placement Error) a partire dagli anni 2010 e le previsioni per il futuro. Fouquet ha notato che le metal pitches si sono ridotte a un tasso del 50% negli ultimi sei anni fino al 2020, ma questo tasso rallenterà e raggiungerà la saturazione nel 2030 (come mostrato nella figura seguente).

Finora, i nomi dei nodi (usati dalle fabbriche di wafer per denotare la miniaturizzazione, indicati in verde nella parte inferiore della figura) si sono allineati con la larghezza minima della linea del filo metallico (linea blu), ma recentemente si è verificata una discrepanza maggiore.

Come abbiamo appena visto, ASML prevede di fornire il primo sistema commerciale EUV ad alto NA (NA=0,55) per scopi di prototipazione entro la fine del 2023, con apparecchiature per la produzione in volumi a partire dal 2025. Pertanto, a partire dal 2025 circa, i clienti saranno in grado di passare dall’utilizzo degli strumenti di litografia EUV con NA = 0,33 per pattern multipli, all’utilizzo di pattern singoli con strumenti di litografia EUV ad alto NA, con conseguente riduzione dei costi di processo e aumento della resa.

A partire dalla fine del decennio, la modellazione multipla con strumenti EUV ad alto NA verrà eseguita insieme alla modellazione singola per migliorare la resa e ridurre i costi, richiedendo apparecchiature di esposizione EUV con NA ancora più elevata (NA = 0,75).

Il prezzo di queste apparecchiature, pur garantendo un abbassamento dei costi di produzione e una maggiore capacità produttiva dei chip sub-2 nm, potrebbe essere troppo elevato anche per i principali produttori globali. La produzione di sistemi Hyper EUV NA, in ultima analisi, dipenderà dall’andamento del mercato e dalla domanda dei clienti.