Intel annuncia di aver completato l’installazione del primo scanner litografico TWINSCAN EXE:5000 High NA presso il sito di ricerca e sviluppo di Hillsboro, Oregon che consentirà all’azienda di produrre i nodi più avanzati della sua roadmap tecnologica.

Alcuni mesi fa, Intel aveva ricevuto da ASML il primo scanner litografico EUV ad elevata apertura numerica (High NA), il primissimo modello commerciale realizzato con la tecnologia di punta dell’azienda olandese che Intel intende utilizzare per la produzione di processori avanzati con nodo di processo 18A (1,8 nm), 14A (1,4 nm) e 10A (1 nm), quest’ultimo da poco aggiunto alla roadmap dell’azienda.

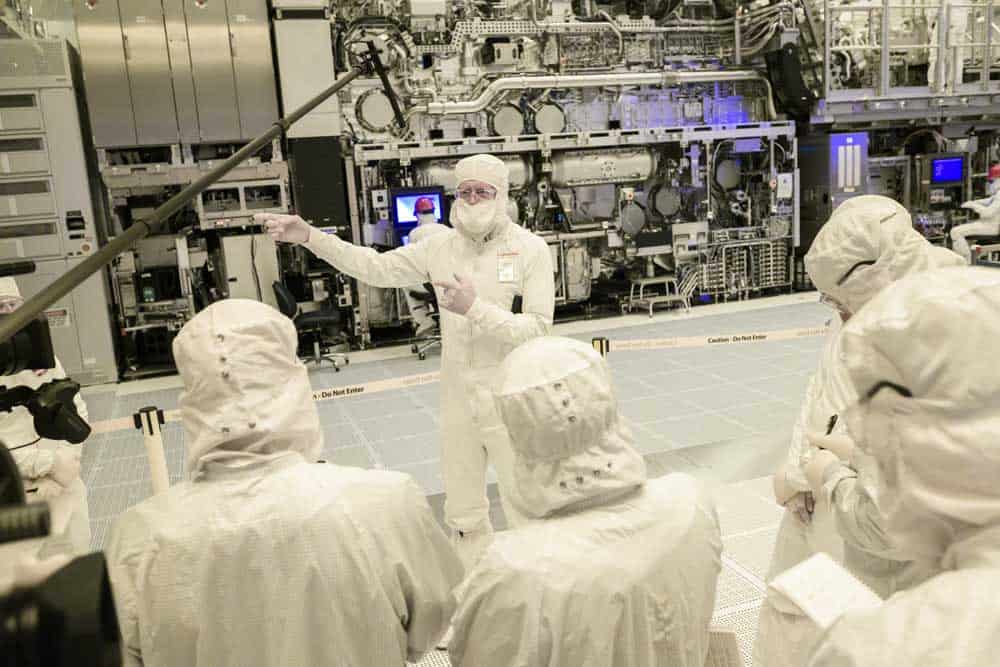

Ieri, durante un incontro con i rappresentati della stampa specializzata che hanno visitato l’impianto, Intel ha annunciato che l’assemblaggio dell’enorme apparecchiatura è praticamente terminato e che sta per iniziare la fase di calibrazione in preparazione dei primi test di produzione.

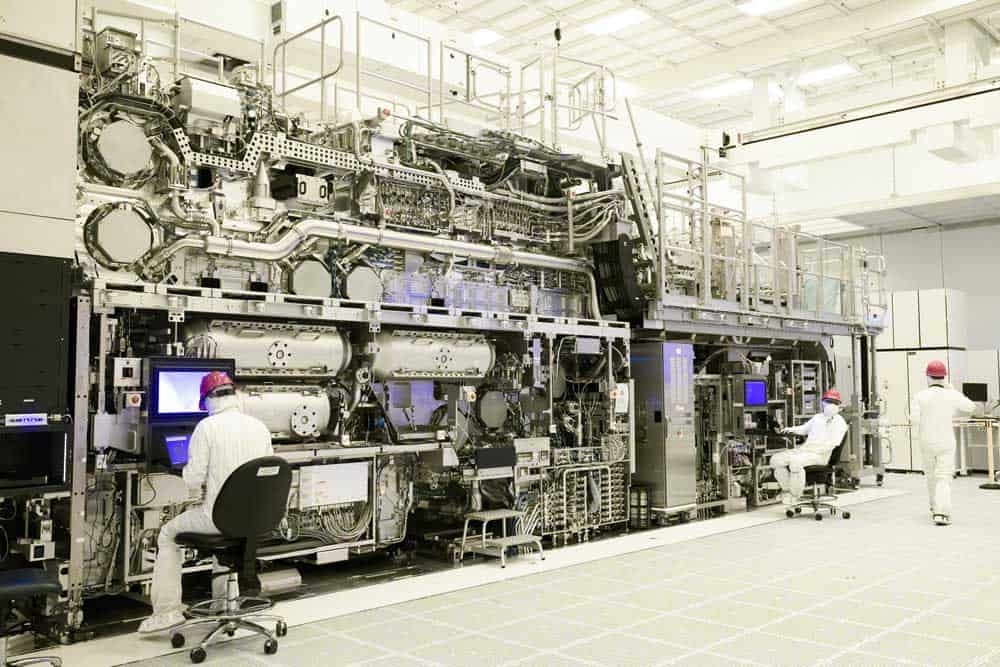

Il sistema TWINSCAN EXE:5000 – fa sapere Intel – è stato trasportato nello stabilimento di ricerca e sviluppo D1X di Hillsboro, Oregon, in più di 250 casse all’interno di 43 container. I container sono stati trasportati dall’Olanda con più aerei cargo atterrati a Seattle; sono stati poi trasferiti con 20 camion fino allo stabilimento di Intel. Il nuovo sistema litografico è grande quanto un autobus a due piani, pesa oltre 150 tonnellate e costa 380 milioni di dollari.

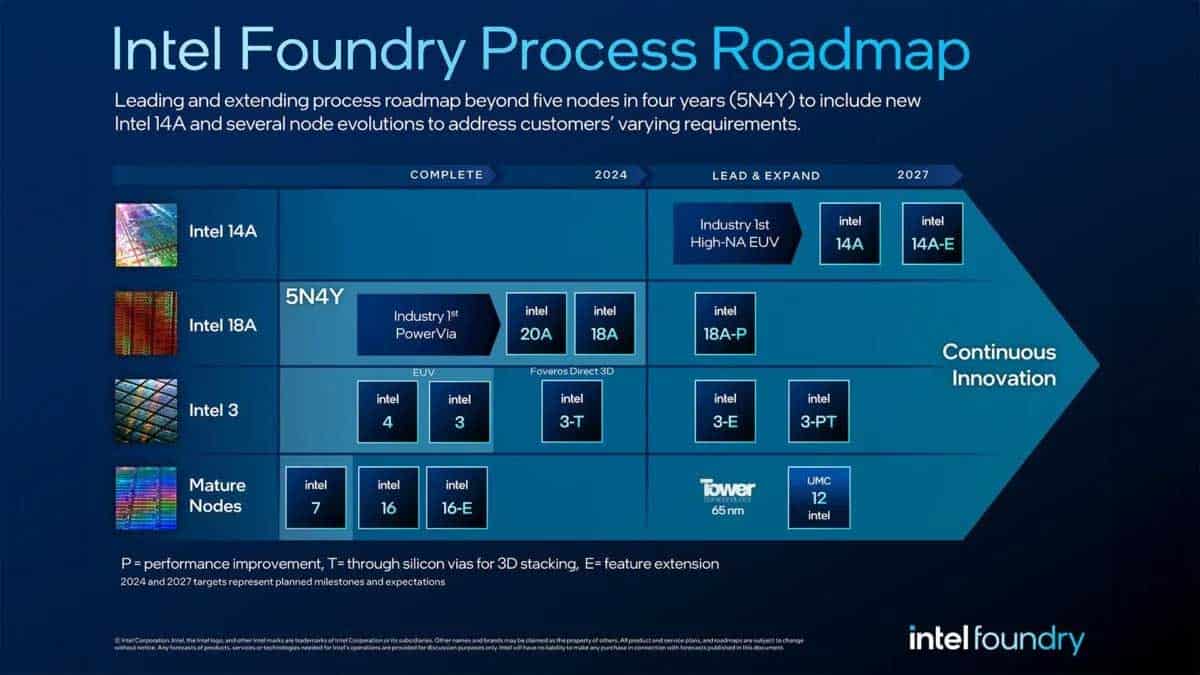

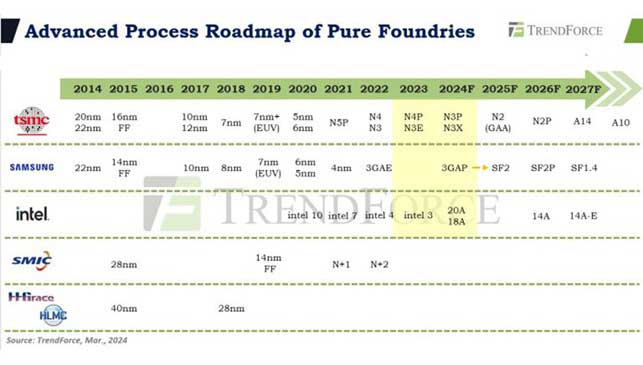

Intel intende utilizzare il sistema di litografia di nuova generazione sviluppato da ASML, frutto anche della collaborazione decennale tra le due aziende, per supportare la sua roadmap nei nodi di processo più avanzati, annunciata e fortemente voluta da Pat Gelsinger che nel 2021 ha preso le redini di un’azienda in grave crisi produttiva, finanziaria e, soprattutto, tecnologica, surclassata dalla taiwanese TSMC e dalla coreana Samsung per quanto riguarda la produzione di semiconduttori avanzati.

L’intenzione ultima di Intel, che ha scorporato le attività di progettazione e sviluppo da quelle produttive creando una divisione completamente autonoma (Intel Foundry Services, IFS), è quella di competere con la sua nuova divisione con i leader del settore TSMC e Samsung.

Pat Gelsinger ha annunciato poco dopo il suo insediamento la roadmap 5N4Y, recentemente aggiornata, per sviluppare cinque nodi produttivi in 4 anni, che dovrebbe fare di IFS la seconda foundry mondiale entro il 2030, alle spalle di TSMC ma davanti a Samsung.

Attualmente, Intel ha completato la transizione a Intel 7, l’ultimo nodo che utilizza la tecnologia DUV, e verso Intel 4, il primo nodo dell’azienda a sfruttare la tecnologia EUV.

La scelta di utilizzare la tecnologia DUV con il supporto del multi-patterning con le relative complicazioni tecniche per realizzare il nodo a 10/7 nm, anziché la tecnologia EUV, è stata una delle ragioni principali del ritardo accumulato da Intel nei confronti di TSMC e Samsung che l’hanno preceduta nell’utilizzo della tecnologia EUV.

Intel 7 è il nome con cui l’azienda chiama il suo processo a 10 nm e Intel 4 è il nome con cui l’azienda chiama il processo a 7 nm; i nomi scelti (secondo le speculazioni degli analisti) stanno ad indicare che il nodo Intel 7 ha una densità di transistor molto simile a quella a 7 nm di TSMC nonostante sia costruito con un processo a 10 nm. Lo stesso discorso vale per Intel 4, che dovrebbe avere la stessa densità del nodo 4/5 nm di TSMC e Intel 3 che è molto simile al nodo N3E a 3 nm di TSMC.

Intel 7 è stato utilizzato per produrre Alder Lake, Raptor Lake e Raptor Lake Refresh, versione che sarà molto probabilmente l’ultimo sviluppo di Intel 7.

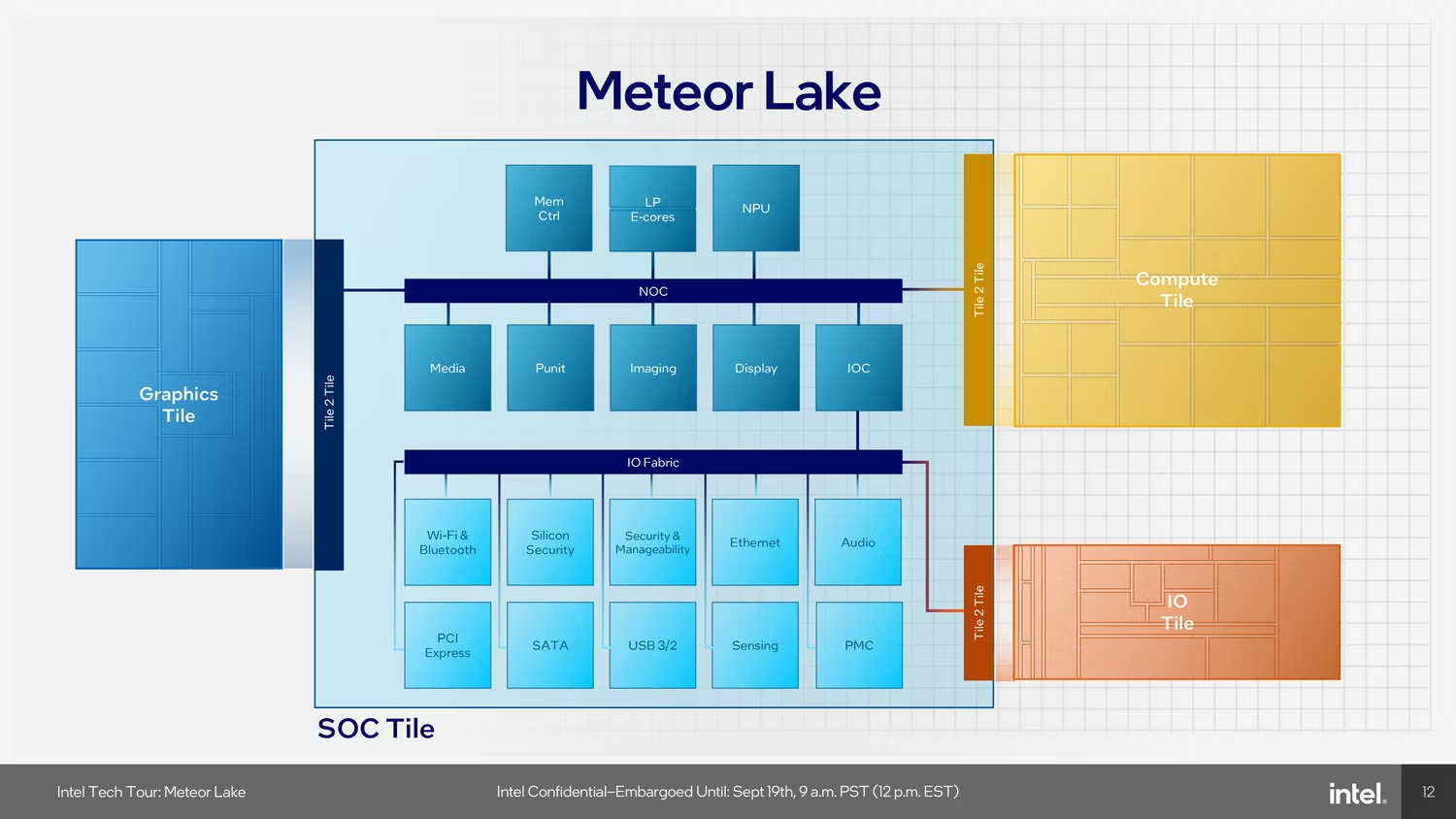

Il nodo a 4 nm Intel 4 viene utilizzato per fabbricare la Computer Tile con core x86 del nuovo processore Meteor Lake, il primo di Intel ad utilizzare una soluzione chiplet anziché un unico die monolitico. La Computer Tile x86 viene infatti integrata sfruttando la tecnologia Foveros 3D con la SOC Tile e la I/O Tile fabbricate da TSMC con processo a 6 nm e con la Graphic Tile anch’essa fabbricata da TSMC ma con processo a 5 nm (in precedenza si era parlato dell’utilizzo del processo a 3 nm). L’interposer utilizza il processo Intel 16.

Del processo Intel 3 si sa ancora poco, salvo il fatto che verrà utilizzato sui sistemi per data center Sierra Forest e Granite Rapids e che offrirà prestazioni per watt superiori del 18% rispetto ad Intel 4.

Ma è con i successi nodi di processo 20A (2 nm), 18A (1,8 nm) e 14A (1,4 nm) che Intel intende raggiungere la “parità di processo” con i competitor asiatici; in particolare il nodo 14A sarà il primo ad utilizzare lo scanner litografico TWINSCAN EXE:5000 appena installato a Hillsboro. Per la produzione con volumi più elevati, Intel riceverà l’anno prossimo la versione avanzata TWINSCAN EXE:5200B (sempre un EUV-NA) con una capacità di 200 wph.

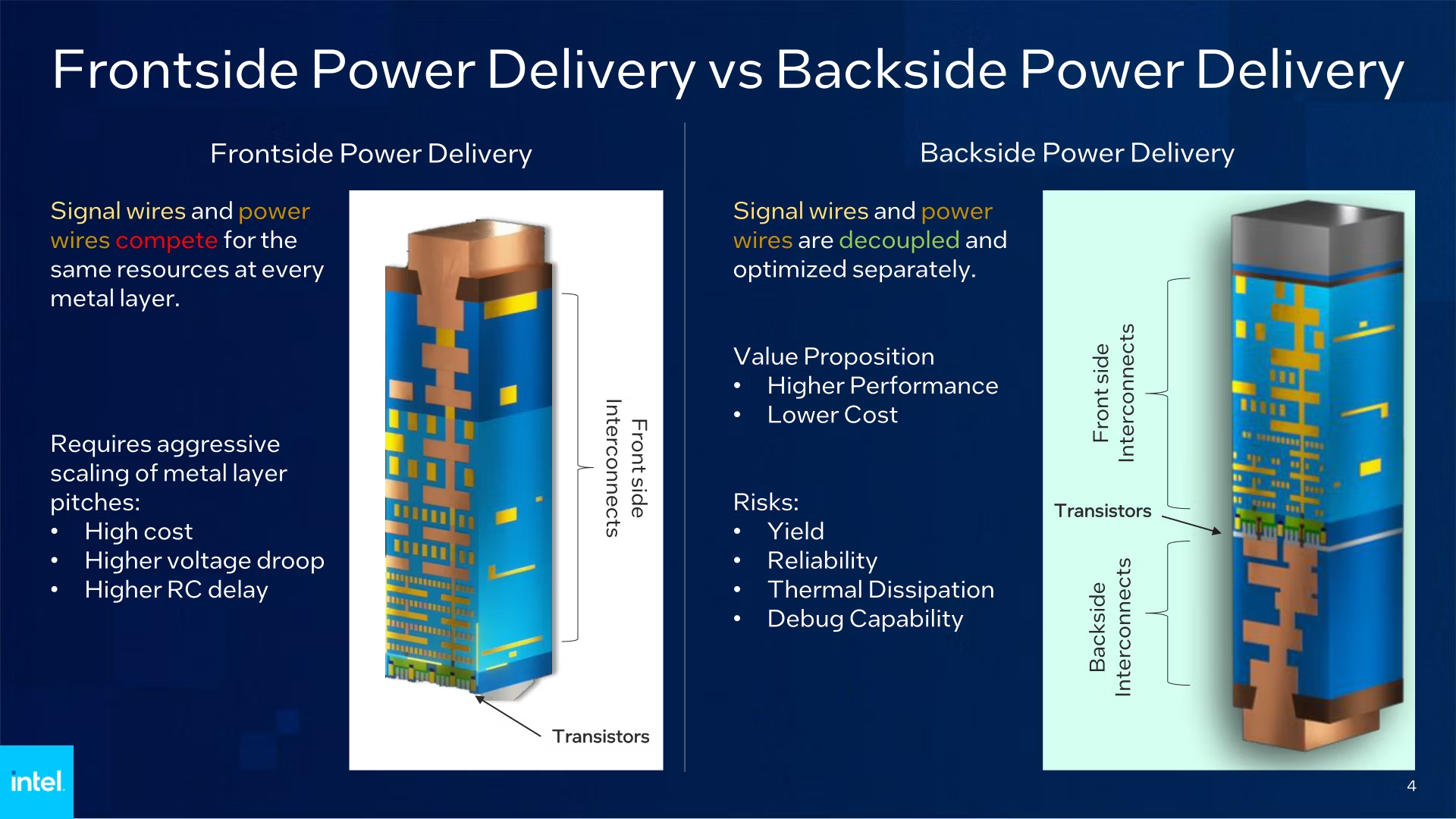

Tutto il settore sta attualmente accelerando sul nodo di processo a 2 nm con Intel che intende fare debuttare Arrow Lake entro la fine dell’anno utilizzando il suo nodo di processo 20A e che utilizzerà per la prima volta sia la tecnologia RibbonFET che quella PowerVia.

Intel PowerVia è una tecnologia innovativa sviluppata da Intel per migliorare le prestazioni. A differenza dei tradizionali chip, dove i transistor e le interconnessioni di alimentazione condividono lo stesso strato, PowerVia separa questi due processi. I transistor vengono realizzati per primi, e solo successivamente vengono aggiunti gli strati di interconnessione sulla parte posteriore del chip.

Questa separazione consente di risolvere il problema dei colli di bottiglia nelle interconnessioni. L’alimentazione dalla parte posteriore del chip è fondamentale per ridurre le dimensioni dei transistor, consentendo ai progettisti di aumentare la densità senza sacrificare risorse per fornire più potenza e prestazioni.

In breve, Intel PowerVia rappresenta un modo completamente nuovo di produrre CPU, migliorando sia le prestazioni che l’efficienza energetica dei microprocessori.

Se Intel utilizzerà il nodo 20A per realizzare i suoi processori, TSMC col suo nodo a 2 nm punterà inizialmente sui processori per gli iPhone di Apple, per poi aumentare velocemente la capacità produttiva a favore di tutti gli altri suoi clienti. L’impianto Fab20 P1 di TSMC a Hsinchu, Baoshan, sta ultimando l’installazione delle apparecchiature per avviare la produzione pilota nel 2H24 e successivamente la produzione in volumi dal 2Q25. Anche per TSMC il nodo N2 sarà il primo con la tecnologia GAAFET.

Della partita fanno parte anche Samsung e la nuova arrivata giapponese Rapidus.

Per quanto riguarda Samsung, la roadmap tecnologica precedentemente annunciata indica che produrrà chip con processo a 2 nm in volumi per terminali mobili a partire dal 2025, seguito da prodotti HPC (High Performance Computing) nel 2026 e dai chip automobilistici entro il 2027.

Rapidus sta allestendo una fabbrica di chip da 2 nm a Chitose City, Hokkaido, in Giappone. La sua linea di produzione pilota dovrebbe entrare in funzione nell’aprile 2025, con l’obiettivo di iniziare la produzione di massa nel 2027.

Il nodo successivo di Intel, 18A, sarà una evoluzione del precedente 20A con un aumento delle prestazioni del 10%. Originariamente questo nodo doveva essere realizzato con i nuovi scanner High NA ma un leggero anticipo sulla tabella di marcia ha convinto Intel ad utilizzare le stesse macchine EUV impiegate per il nodo 20A. In questo modo l’azienda riuscirà a produrre i primi chip con questo processo entro la fine del 2024. Intel utilizzerà questa tecnologia per produrre una versione consumer della CPU Lake e la Panther Lake per data center con P-core Cougar Cove e, probabilmente, anche con E-core con architettura Darkmont.

Sarà dunque il nodo di processo 14A il primo che verrà realizzato con il nuovo TWINSCAN EXE:5000 High NA che sta per entrare in funzione presso il fab D1X di Intel.

TWINSCAN EXE:5000 High NA, l’impianto industriale più complesso al mondo

Tale è considerato da molti il nuovo scanner per litografia a raggi ultravioletti estremi (EUV) ad alta apertura numerica (High NA) di ASML, una macchina che ha la capacità di migliorare notevolmente lo scaling delle funzionalità di risoluzione per i processori di prossima generazione e che manterrà in vita la Legge di Moore per molti anni ancora.

“Con l’aggiunta di High NA EUV, Intel disporrà del toolbox di litografia più completo del settore, consentendo all’azienda di portare le future capacità di processo oltre Intel 18A nella seconda metà di questo decennio”, ha dichiarato Mark Phillips, Intel Fellow and director of Lithography, Hardware and Solutions for Intel Foundry Logic Technology Developmen.

A conferma delle possibilità offerte dalla nuova tecnologia, mentre Intel è alle prese con la calibrazione della sua prima macchina, ASML ha annunciato di aver stampato le prime linee dense di 10 nanometri (nm) nel laboratorio High NA presso la sede dell’azienda a Veldhoven, nei Paesi Bassi. Queste sono le linee più fini mai stampate, che stabiliscono una risoluzione da record per uno scanner litografico EUV. Questa dimostrazione convalida l’innovativo design dell’ottica High NA EUV del partner di ASML Zeiss.

Immagini rivoluzionarie sono state stampate dopo che l’ottica, i sensori e le fasi dello strumento hanno completato la calibrazione grossolana: un trampolino di lancio per il funzionamento con specifiche complete. La capacità di ASML di stampare linee dense di 10 nm con un sistema di litografia ottica a tutto campo è un passo fondamentale verso la preparazione dello strumento High NA EUV per l’uso commerciale.

Intel prevede che, se combinata con le altre funzionalità tecnologiche di processo, la tecnologia High NA EUV sarà in grado di stampare caratteristiche fino a 1,7 volte più piccole rispetto agli strumenti EUV esistenti. Ciò consentirà il ridimensionamento delle funzionalità 2D, con conseguente densità fino a 2,9 volte maggiore.

Rispetto agli attuali strumenti EUV, l’evoluzione High NA è in grado di fornire un contrasto di immagine più elevato per caratteristiche simili, che consente l’utilizzo di meno luce per esposizione, riducendo così il tempo necessario per stampare ogni strato e aumentando la resa del wafer.

Intel prevede di acquistare l’anno prossimo il sistema TWINSCAN EXE:5200B di prossima generazione che consente di aumentare la produttività ad oltre 200 wafer all’ora.

Come funziona la tecnologia High NA EUV

La tecnologia litografica High NA EUV utilizza una lunghezza d’onda della luce (13,5 nm) che non si trova naturalmente sulla Terra. La luce viene creata da un potente laser che colpisce una goccia di stagno riscaldata a una temperatura di quasi 220.000 gradi Celsius, quasi 40 volte più calda della temperatura superficiale media del sole. Questa luce si riflette su una maschera contenente il modello circuitale desiderato per poi, attraverso un sistema ottico costruito con gli specchi più accurati mai fabbricati, incidere lo strato di fotoresist depositato sulla superficie del wafer.

L’apertura numerica (NA) è una misura della capacità di raccogliere e focalizzare la luce. Modificando il design dell’ottica utilizzata per proiettare un modello su un wafer, la tecnologia High NA EUV consente un significativo passo avanti nella risoluzione e nelle dimensioni dei transistor. La capacità di creare transistor di dimensioni più piccole richiede anche nuove strutture di transistor e miglioramenti in altre fasi del processo che Intel sta sviluppando parallelamente all’integrazione del primo sistema High NA EUV.