Una soluzione di protezione di ingresso affidabile per server AI a 48 V che elimina le limitazioni dei controller hot-swap legacy.

Con i progressi nell’intelligenza artificiale (IA) e nell’apprendimento automatico, i server aziendali sono diventati estremamente esigenti in termini di energia, poiché elaborano contemporaneamente una grande quantità di dati e storage. La potenza nominale in stato stazionario di ciascuna scheda madre del server è salita a 5÷6 kW rispetto a 1÷2 kW per i server generici. Il fattore di forma rimane tuttavia invariato, il che impone sfide di progettazione del sistema data la maggiore densità di potenza. L’ampiezza del carico, la velocità di risposta e la frequenza dei carichi transitori sui server AI sono aumentati da tre a quattro volte rispetto ai server generici.

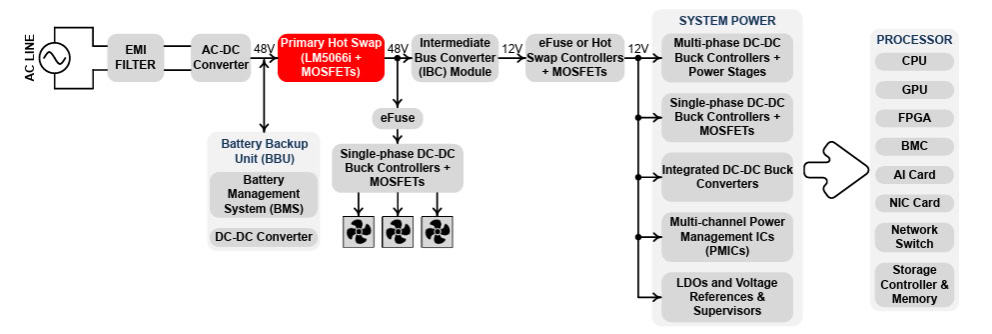

La Figura 1 mostra una tipica distribuzione dell’alimentazione in un server rack a 48 V, in cui l’ingresso è protetto dal circuito hot-swap e quindi distribuito a tutti i carichi del sistema a valle.

Figura 1. Tipico schema a blocchi della distribuzione dell’alimentazione di un server rack a 48 V.

In questo articolo, discuteremo le varie sfide che i processori basati su intelligenza artificiale (IA) pongono nei progetti di server a 48 V, insieme a linee guida di progettazione e importanti suggerimenti e trucchi per la progettazione e il layout, al fine di ottenere una soluzione hot-swap affidabile per le specifiche di sistema descritte nella Tabella 1.

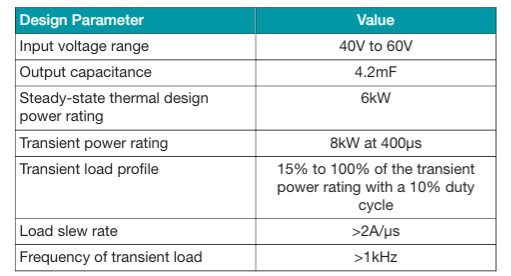

Tabella 1. Tipiche specifiche di sistema.

Sfide nella progettazione di un circuito hot-swap per un server IA a 48 V

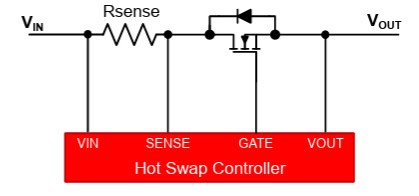

È interessante osservare come le configurazioni dei circuiti hot-swap si siano evolute nel corso degli anni. Una soluzione hot-swap è composta da tre componenti principali: un transistor MOSFET a canale N che funge da interruttore di controllo dell’alimentazione principale; una resistenza di rilevamento che misura la corrente; e il controller hot-swap, che include un amplificatore di rilevamento della corrente che completa il loop per controllare la corrente di passaggio del MOSFET.

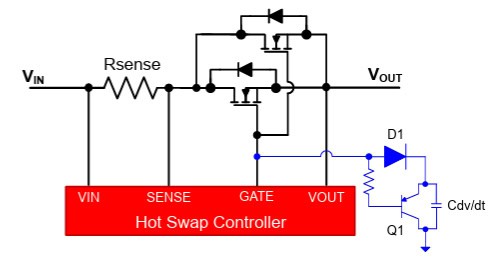

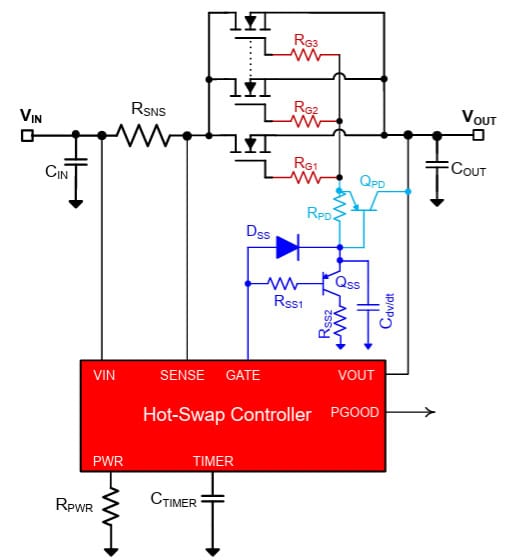

Come mostrato in Figura 2, è possibile utilizzare una soluzione hot-swap basata su un singolo MOSFET per progetti a bassa potenza.

Fondamentalmente, il controller hot-swap è dotato di funzionalità di limitazione di corrente e potenza per limitare le correnti di spunto e di guasto, garantendo al contempo l’area operativa sicura (SOA) del MOSFET. Queste funzionalità sono sufficienti per progettare soluzioni hot-swap a bassa potenza (<500W).

Figura 2. Circuito hot-swap tradizionale con limitazione di potenza.

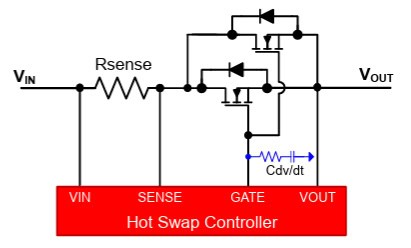

Figura 3. Circuito hot-swap con controllo della velocità di risposta del GATE.

Figura 4. Circuito hot-swap con percorso di scarica locale per Cdv/dt.

Con l’aumento del carico digitale, il sistema necessita di una capacità di uscita maggiore (>470µF), richiedendo MOSFET paralleli per supportare la corrente a regime stazionario e l’adozione del controllo della velocità di variazione della tensione di uscita per mantenere il MOSFET entro la sua SOA.

Nel metodo di controllo della velocità di variazione della tensione di uscita, il condensatore Cdv/dt posizionato tra GATE-GND (vedere Figura 3) limita la velocità di variazione delle tensioni di gate e di uscita, limitando di conseguenza la corrente di spunto. I MOSFET possono gestire più energia quando la dissipazione di potenza al loro interno viene ridotta e distribuita su periodi di tempo più lunghi. Pertanto, all’aumentare della capacità di uscita, è necessario un Cdv/dt più elevato per ridurre sia la corrente di spunto che la dissipazione di potenza nel MOSFET durante l’avvio.

Un Cdv/dt più elevato interferisce con il processo di spegnimento, tuttavia, il controller hot-swap ha una forza di pulldown limitata. Ciò richiede un circuito di scarica locale basato su P-channel (PNP) per Cdv/dt, come mostrato in Figura 4. Durante l’avvio, Cdv/dt controlla lo slew-rate allo stesso modo, ma durante un evento di spegnimento, il

transistor PNP Q1 si attiva e scarica Cdv/dt localmente. Il diodo D1 blocca la scarica di Cdv/dt sul pin GATE, riducendo lo stress sul pin GATE e garantendo anche il corretto funzionamento del controller. Nelle applicazioni con unità di elaborazione grafica basate sull’intelligenza artificiale, la soluzione hot-swap deve supportare correnti intorno ai 150 A e transitori di carico ad alta frequenza e alta velocità di variazione, che presentano tre nuove sfide.

Sfida n. 1: Ritardo di spegnimento durante un cortocircuito in uscita

Con l’aumento della corrente di carico, è necessario collegare in parallelo più MOSFET per limitare la temperatura massima di giunzione del MOSFET in stato stazionario a un valore di sicurezza (da 100 °C a 125 °C).

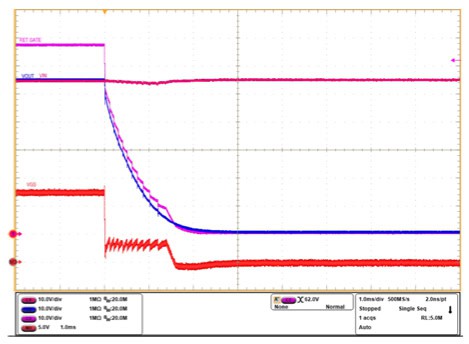

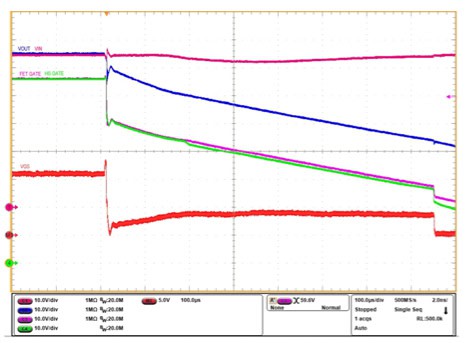

Ad esempio, per supportare una corrente di carico in stato stazionario di 150 A ad una temperatura ambiente di 70 °C, otto MOSFET CSD19536KTT di Texas Instruments devono essere collegati in parallelo per limitare la temperatura di giunzione del MOSFET in stato stazionario a 100 °C. I MOSFET in parallelo aiutano dal punto di vista termico, ma aumentano la capacità effettiva sul pin GATE del controller hot-swap e influiscono sulla risposta allo spegnimento. Durante un cortocircuito in uscita, i MOSFET devono spegnersi rapidamente in modo da impedire un ulteriore accumulo di corrente di guasto e da evitare danni ai MOSFET, all’alimentatore di ingresso o al circuito stampato (PCB). La corrente di pull-down del gate del controller hot-swap TI LM5066I è limitata a 160 mA, un valore insufficiente per spegnere completamente tutti gli otto MOSFET durante un cortocircuito, come mostrato in Figura 5.

Figura 5. Risposta al cortocircuito del controller LM5066I con otto MOSFET.

Figura 5. Risposta al cortocircuito del controller LM5066I con otto MOSFET.

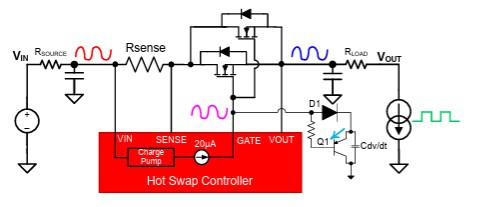

Sfida n. 2: Falso spegnimento del gate durante un transitorio di carico

Sebbene il circuito di scarica locale basato su PNP per Cdv/dt aiuti a spegnere in modo affidabile i MOSFET durante un cortocircuito in uscita, può essere causa un falso spegnimento del GATE in presenza di transitori di carico ad alta frequenza e alta velocità. Durante l’aumento del carico, il nodo source del MOSFET si abbassa a causa delle impedenze di ingresso e di uscita finite del circuito hot-swap. La caduta di tensione

sul nodo source viene accoppiata al nodo gate del MOSFET attraverso la capacità CGS del MOSFET e provoca anche la caduta del nodo gate. Il nodo source del MOSFET si ripristina durante l’abbassamento del carico. Il nodo gate non può tornare completamente al livello precedente a causa della corrente di gate limitata (tipicamente 20 µA) del controller hot-swap LM5066I. Di conseguenza, il gate del controller hot-swap continua a scendere ulteriormente nei successivi cicli transitori di carico, sviluppando la tensione base-emettitore per Q1. Infine, il transistor bipolare PNP Q1 si accende e spegne erroneamente il sistema. La Figura 6 illustra l’intero processo, mentre la Figura 7 mostra il risultato del test corrispondente.

Figura 6. Illustrazione di un circuito hot-swap per un carico dinamico.

Figura 7. Risposta di un circuito hot-swap a un carico dinamico.

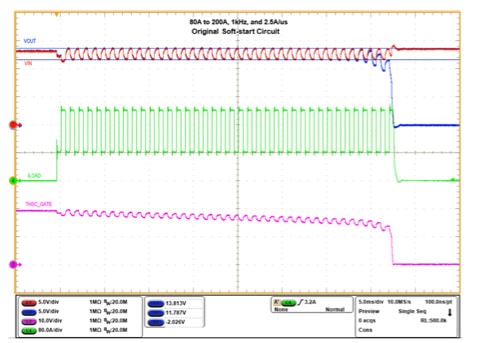

Sfida n. 3: Risonanza parallela durante l’accensione controllata (lenta)

In genere, i MOSFET paralleli sono più inclini alle oscillazioni parassite rispetto a un singolo MOSFET nella regione lineare

di funzionamento. Ciò è dovuto alla presenza di induttanze e capacità parassite del package sui nodi di drain, source e gate, che formano un circuito a serbatoio risonante simile a un oscillatore Colpitts. A differenza dei regolatori switching con una corrente di gate-drive >2A, i controller hot-swap con una corrente di gate-drive inferiore (20µA) limitano la corrente di spunto durante l’avvio facendo funzionare i MOSFET nella regione lineare. Di conseguenza, la combinazione in parallelo di MOSFET hot-swap è altamente suscettibile, con maggiori probabilità di generare oscillazioni sostenute. Questo fenomeno causa la violazione del SOA del MOSFET durante un guasto di tipo “power-into-short”, con conseguente danneggiamento del MOSFET.

Miglioramenti circuitali proposti

Esaminiamo i miglioramenti circuitali per contribuire a risolvere queste tre sfide.

Miglioramento della risposta allo spegnimento

Nella soluzione proposta mostrata in Figura 8, l’introduzione di un circuito esterno di pull-down rapido che utilizza transistor PNP (QPD e RPD) aumenterà la velocità di spegnimento. Durante un cortocircuito in uscita, la corrente di pull-down del gate di 160mA crea una caduta di tensione sostanziale ai capi del resistore RPD e consente il pull-down rapido del transistor PNP (QPD). Questo a sua volta cortocircuita il gate-source di tutti i MOSFET in parallelo, spegnendo immediatamente i MOSFET e scollegando rapidamente il percorso di alimentazione. La Figura 9 mostra il risultato sperimentale di un evento di cortocircuito con un circuito di pull-down rapido.

Superamento del falso spegnimento per carichi dinamici

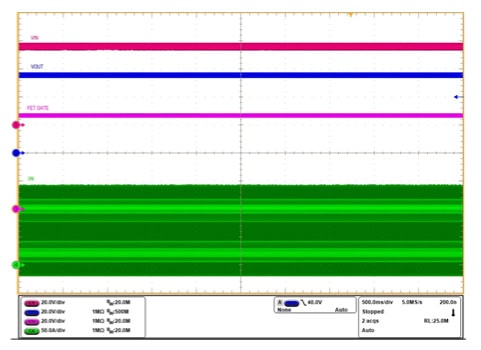

In questa soluzione, il nodo del gate hot-swap viene disaccoppiato dal terminale del gate del MOSFET posizionando il diodo DSS tra di essi, come mostrato di nuovo in Figura 8. Questa modifica aiuta a eliminare la riflessione dell’ondulazione della tensione di uscita sul nodo GATE del controller hot-swap ed evita il falso spegnimento del transistor PNP di soft-start, Qss. La modifica della posizione del diodo non influisce sul comportamento del controller durante l’avvio né su alcun evento di guasto. Come mostrato nel risultato del test (vedere Figura 10), il sistema funziona ininterrottamente anche per grandi incrementi di carico da 20 A fino a 120 A ad una frequenza di 1 kHz.

Figura 8. Configurazione del circuito hot-swap proposta.

Figura 8. Configurazione del circuito hot-swap proposta.

Figura 9. Risposta al cortocircuito in uscita con circuito di pull-down rapido.

Figura 10. Prestazioni transitorie del carico per variazioni da 20 A a 120 A e a 20 A, con una frequenza di 1 kHz.

Figura 10. Prestazioni transitorie del carico per variazioni da 20 A a 120 A e a 20 A, con una frequenza di 1 kHz.

Smorzamento delle oscillazioni parassite

L’aggiunta di una resistenza di smorzamento (RG1, RG2, RG3) in serie al gate di ciascun MOSFET può eliminare le oscillazioni parassite nel sistema. Solitamente, si consiglia una resistenza in formato 0603 da 10 Ω, ma in base alle oscillazioni parassite, anche un valore basso, intorno a 1 Ω, può essere d’aiuto. Si consiglia di effettuare dei test sul PCB e di determinare il valore della resistenza di smorzamento.

Linee guida di progettazione e selezione dei componenti

Il documento [1] illustra una procedura per la progettazione di un circuito hot-swap per proteggere il sistema e i MOSFET. Si consiglia di consultare questo documento per acquisire familiarità con il progetto. Inserendo le specifiche di sistema mostrate nella Tabella 1 nel calcolatore di progetto LM5066I, si otterranno i valori della resistenza di rilevamento della corrente (RSNS), della resistenza di limitazione della potenza (RPWR), del condensatore del timer di guasto (CTIMER), del condensatore di soft-start (Cdv/dt) e il numero (N) di MOSFET selezionati da collegare in parallelo. Nel progetto di riferimento per hot-swap da 8 kW per server di intelligenza artificiale a 48 V [vedi documento 2], RSNS = 330 µΩ, RPWR = 28,7 kΩ, CTIMER = 10 nF, Cdv/dt = 47 nF e N =8.

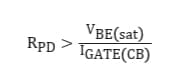

Considerando la Figura 8, selezionare la resistenza RPD utilizzando l’Equazione:

dove VBE(sat) è la tensione di saturazione base-emettitore del transistor PNP QPD e IGATE(CB) è la corrente di dissipazione dell’interruttore di reset all’accensione nel controller hot-swap LM5066I. Il progetto di riferimento hot-swap da 8 kW utilizza un valore RPD = 20 Ω.

Circuito di scarica Cdv/dt

La Figura 8 utilizza un diodo di segnale da 100 V per DSS. Il diodo dovrebbe gestire alcune decine di milliampere di corrente diretta. Il progetto di riferimento hot-swap da 8 kW utilizza il BAV16W-7-F di Diodes Inc.

Sarà necessario selezionare RSS1, RSS2 e QSS in modo iterativo in modo che nessuno dei tre componenti venga sollecitato durante lo spegnimento. Per QSS, è possibile selezionare qualsiasi transistor PNP standard con tensioni collettore-emettitore (VCEO) e collettore-base (VBEO) >100 V DC e una corrente di collettore continua >200 mA. Selezionare i valori per RSS1 e RSS2 e le rispettive potenze nominali per limitare la corrente che scorre attraverso il transistor QSS a un valore sicuro.

È necessario utilizzare una speciale resistenza ad alta potenza per RSS2 per gestire lo stress di potenza di picco transitorio durante lo spegnimento. Il progetto di riferimento hot-swap da 8 kW utilizza un semiconduttore MMBT5401LT1G per QSS, con RSS1 = 100Ω e RSS2 = 499Ω (Vishay RCS0805499RFKEA).

I diodi di soppressione della tensione transitoria (TVS) in ingresso sono necessari per proteggere dalle sovratensioni transitorie durante gli eventi di hot-plug in ingresso e cortocircuito in uscita. Lo strumento TVS Diode Recommendation tool di TI può aiutare a ottenere il codice prodotto (tensione e potenza nominale) del diodo TVS e il numero di diodi TVS da collegare in parallelo. Il progetto di riferimento hot-swap da 8 kW utilizza tre diodi TVS Littelfuse 8.0SMDJ60A. Per un’analisi più approfondita sulla selezione dei diodi TVS, vedere il documento di riferimento [3].

Saranno necessari diodi Schottky di uscita per proteggere il pin di uscita del controller hot-swap da un transitorio negativo in caso di cortocircuito in uscita. Il progetto di riferimento hot-swap da 8 kW utilizza tre diodi Schottky onsemi FSV20100V.

Conclusione

I server AI emergenti a 48 V richiedono una potenza significativamente maggiore, sia in condizioni di picco che stazionarie, rispetto ai server tradizionali. L’elevato consumo energetico, unito alla dinamica rapida e transitoria, impone sfide nella progettazione della protezione front-end utilizzando un controller hot-swap e MOSFET paralleli. Le sfide includono lo spegnimento rapido dei MOSFET paralleli in caso di guasti reali, evitando al contempo lo spegnimento involontario per transitori ad alta frequenza dovuti al carico computazionale. La soluzione proposta in questo articolo elimina le limitazioni dei controller hot-swap legacy e consente la progettazione di una soluzione di protezione di ingresso affidabile per un server AI a 48 V.

Documenti di riferimento

- Rogachev, Artem. “Robust Hot Swap Design.” Texas Instruments application report, literature No. SLVA673A, April 2014.

- Texas Instruments. “8kW Hot-Swap Reference Design for 48V Artificial Intelligence Servers.” Texas Instruments test report, literature No. PMP23496, August 2024.

- Hegarty, Timothy. 2011. “TVS Clamping in Hot-Swap Circuits.” Power Electronics Technology, October 2011.

Avishek Pal è Applications Engineer, eFuse & Hot Swap Controllers presso Texas Instruments; Rakesh Panguloori è Research Engineer presso Philips Research Asia, Philips, Bangalore.