Nell’articolo viene anche illustrato come utilizzare la decimazione per facilitare la pianificazione delle frequenze e come proteggere la banda dal cadere in un “buco” di frequenza durante la fase di progettazione e sviluppo.

La pianificazione delle frequenze è fondamentale per qualsiasi applicazione basata sulla frequenza. Assicurarsi che la frequenza o le frequenze di interesse siano valide, all’interno della banda e non ridotte al punto da perdere la gamma dinamica spuria dovrebbe essere parte di qualsiasi strategia di sviluppo delle frequenze. In questo articolo, tratteremo le regole di Nyquist dei convertitori analogico-digitali (ADC) ad alta velocità e la loro applicazione al campionamento super-Nyquist. Spiegheremo anche come utilizzare la decimazione per facilitare la pianificazione delle frequenze e come proteggere la banda dal cadere in un “buco” di frequenza durante la fase di progettazione e sviluppo.

Regole di Nyquist

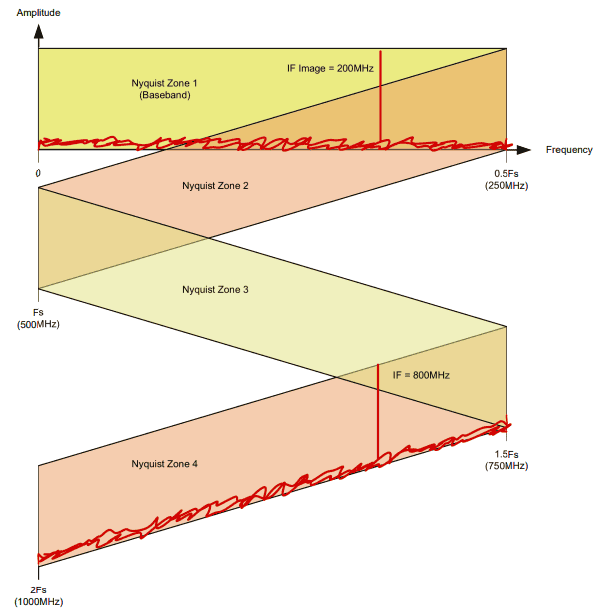

Il campionamento Super Nyquist, il campionamento a frequenza intermedia (IF) e il sottocampionamento sono diffusi in molte applicazioni basate sulla frequenza che impiegano architetture di ricevitori simili a radar o a radio definite dal software (SDR, vedere Figura 1).

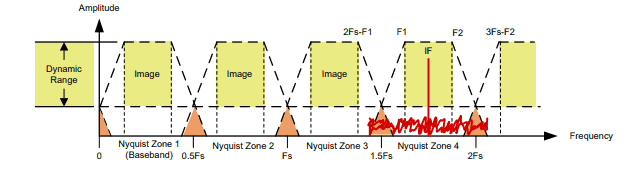

Figura 1. Esempio di un campione super Nyquist rispetto al campionamento in banda base (first Nyquist)

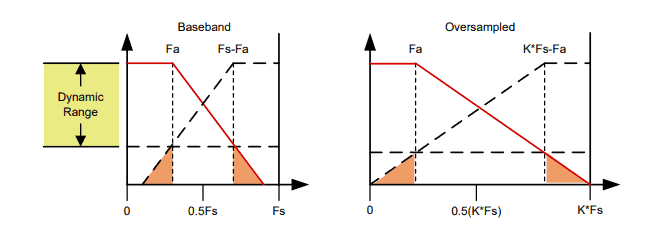

Ci sono due motivi principali per pianificare frequenze al di fuori della banda base (first Nyquist). Il primo motivo è quello di ottenere i vincoli di rilassamento imposti al progetto del filtro antialiasing AAF (vedi Figura 2). Inizialmente, il rolloff generale del filtro deve essere molto più ripido quando si progetta un filtro in banda base rispetto a un filtro progettato per una zona di Nyquist più elevata. Un rolloff più ripido del filtro porta a un filtro più complesso, in cui i componenti passivi diventano ingombranti. È semplice fisica: non è possibile acquistare un induttore da 100 µH in una dimensione 0201. Pertanto, quando si utilizza una zona di Nyquist più elevata, e possibilmente una frequenza di campionamento più elevata, i compromessi e i requisiti per il rolloff nella regione della banda di arresto sono più flessibili, con conseguente riduzione del numero di componenti e delle dimensioni dei componenti.

Il secondo motivo per utilizzare la tecnica di sottocampionamento ad alta frequenza è quello di rilassare la catena del segnale del ricevitore a radiofrequenza (RF) a monte dell’ADC. Supponendo che l’ADC possa supportare i requisiti di larghezza di banda oltre first Nyquist, cosa che accade quasi sempre, rilassare la catena del segnale del ricevitore potrebbe eliminare uno o addirittura due stadi di mixdown nella catena del segnale RF, con conseguente riduzione del numero di componenti, del rumore e della complessità.

Figura 2. Gamma dinamica vs. attenuazione della banda di arresto AAF.

Ad esempio, la Figura 3 mostra l’ADC3669 di Texas Instruments che campiona una frequenza intermedia di 800 MHz rispetto a una frequenza di campionamento (Fs) di 500 MSPS. In sostanza, il segnale si trova nella quarta zona di Nyquist. L’immagine o alias della frequenza di interesse si riflette sulla prima zona di Nyquist, apparendo come un segnale a 200 MHz. La maggior parte degli analizzatori di trasformata di Fourier veloce (FFT), come High-Speed Data Converter Pro, traccia solo una FFT della prima zona di Nyquist, ovvero da 0 Fs a 0,5 Fs. Pertanto, se la frequenza di interesse è superiore a 0,5 Fs, un’immagine si riflette sulla prima zona di Nyquist o sulla prima banda base. Questo può creare confusione se nella banda di interesse sono presenti anche toni spuri.

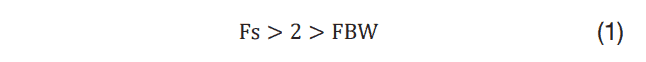

Come fa un convertitore A/D a campionare a una velocità superiore a 0,5 Fs e a rispettare comunque il criterio di Nyquist? La regola di Nyquist stabilisce che un segnale deve essere campionato a una velocità pari o superiore al doppio della sua larghezza di banda per preservare tutte le informazioni del segnale (vedere Equazione 1):

dove Fs è la frequenza di campionamento e FBW è la frequenza massima di interesse.

Figura 3. Esempio con ADC3669, dove Fs = 500 MSPS e frequenza intermedia = 800 MHz.

La chiave per garantire la validità della regola di Nyquist è la posizione delle frequenze di interesse. Finché i segnali non si sovrappongono e rimangono all’interno di una singola zona di Nyquist, il criterio di Nyquist rimane valido. L’unica cosa che è cambiata è la posizione della prima zona di Nyquist in una più alta. Il campionamento IF sta diventando molto popolare proprio grazie a questi compromessi.

Che cosa è il guadagno di processo?

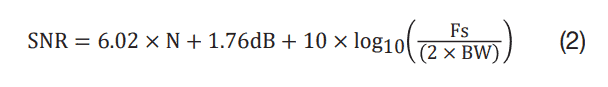

Le prime forme di allineamento della catena del segnale ad alta velocità prevedevano ADC che consumavano watt di potenza per singolo canale e FPGA (Field-Programmable Gate Array) che catturavano, filtravano ed elaboravano tutti i dati del convertitore in un formato utile. La maggior parte dei progettisti utilizzava un approccio chiamato “process gain”. Questo approccio non solo facilitava la pianificazione delle frequenze eliminando spurie e rumore indesiderati, ma consentiva anche di “guadagnare” gamma dinamica in termini di rapporto segnale/rumore (SNR) limitando la larghezza di banda elaborata all’interno della zona di Nyquist. Aggiungendo il fattore di correzione del “process gain” all’equazione standard del SNR si ottiene l’Equazione 2:

dove N è il numero di bit ADC, Fs è la frequenza di campionamento ADC e BW è la larghezza di banda di interesse all’interno della zona di Nyquist.

dove N è il numero di bit ADC, Fs è la frequenza di campionamento ADC e BW è la larghezza di banda di interesse all’interno della zona di Nyquist.

Con l’impiego di nodi di processo più piccoli sia nella tecnologia ADC che in quella di conversione digitale-analogica, gran parte delle funzionalità digitali standard degli FPGA ora risiedono all’interno dell’ADC. Alcuni esempi includono downconverter digitali (DDC), oscillatori a controllo numerico (NCO) e frequency hopping. Queste funzionalità contribuiscono significativamente a ridurre il carico di elaborazione dell’FPGA, consentendo di utilizzare le sue risorse interne altrove.

Perché una pianificazione delle frequenze?

Una corretta pianificazione delle frequenze è un passaggio fondamentale nella progettazione di sistemi che utilizzano convertitori A/D. La pianificazione delle frequenze garantisce un utilizzo efficiente della gamma dinamica del convertitore A/D e riduce al minimo i segnali spuri indesiderati, fondamentali per applicazioni ad alte prestazioni come i sistemi SDR o le catene di segnali RF ad alta densità.

Un aspetto essenziale della pianificazione delle frequenze è l’ottimizzazione della gamma dinamica dell’ADC. Ogni segnale aggiuntivo nel dominio analogico consuma parte del budget di potenza del segnale di ingresso disponibile dell’ADC, riducendo la capacità di gamma dinamica totale. Una corretta pianificazione delle frequenze garantisce che l’ADC esprima appieno le sue capacità posizionando strategicamente le frequenze di ingresso per massimizzare la gamma dinamica utilizzabile. Questo approccio prevede di considerare dove spurie e armoniche indesiderate appariranno nella banda campionata, assicurando che non vi sia sovrapposizione tra i segnali di interesse e le componenti spurie.

Un altro aspetto critico è la gestione dei segnali spuri intrinseci generati dagli ADC, come armoniche e artefatti di interlacciamento. Un piano di frequenza ha successo quando questi contributi spuri rimangono al di fuori della banda desiderata, soprattutto nei sistemi che non utilizzano il filtraggio digitale dopo il campionamento dei dati. La pianificazione delle frequenze aiuta anche a ridurre al minimo l’impatto delle spurie legate al clock, come quelle che provengono da dispositivi di clock privi di isolamento di canale, che sono particolarmente problematiche nei sistemi a elementi di grandi dimensioni che utilizzano una soluzione di distribuzione del clock ad alta densità.

La gestione delle spurie di interlacciamento è anche un aspetto da considerare nei sistemi che contengono un ADC interlacciato, in cui più core ADC campionano un segnale di ingresso comune ortogonalmente, raddoppiando di fatto la frequenza di campionamento e la regione di Nyquist di un fattore due. Questo interlacciamento introduce tuttavia toni spuri a Fs/2-Fin. Inoltre, nei sistemi che utilizzano fattori di interlacciamento più elevati, questa stessa spuria a Fs/2-Fin viene modulata ancora una volta dal “nuovo” Fs/2-Fin. Ciò fa sì che la nuova Fin sia composta dalla spuria Fs/2-Fin interlacciata, il che significa che il numero di spurie introdotto è molto più elevato rispetto a un singolo fattore di interlacciamento.

La pianificazione della frequenza consente di mitigare queste spurie sfruttando il filtraggio analogico o (preferibilmente) i filtri di decimazione digitale, attenuandole in modo significativo senza dover progettare una complessa catena del segnale analogico. Sebbene questo approccio riduca la larghezza di banda istantanea a una regione selezionata, garantisce una migliore gamma dinamica e prestazioni del segnale più pulite.

Errori comuni nella pianificazione delle frequenze

Nonostante i suoi vantaggi, è possibile avere un piano di frequenza non corretto, che può portare a problemi che degradano le prestazioni dell’ADC. Una sfida comune è la sovrapposizione della zona di Nyquist. Segnali di ingresso mal pianificati possono trovarsi ai confini delle zone di Nyquist, causando effetti di aliasing che riducono le prestazioni del sistema. Per evitare ciò, i segnali devono essere allocati all’interno di bande di frequenza appropriate per mantenere l’integrità spettrale con la zona di Nyquist in considerazione. La contaminazione delle spurie di clock è un altro problema frequente, soprattutto nei sistemi che utilizzano dispositivi di clock di bassa qualità o una distribuzione del clock non ottimale. Questi segnali spuri, modulati sullo spettro dell’ADC, possono avere un impatto significativo sulle applicazioni sensibili fornendo una spuria di offset nota. Un’attenta progettazione dell’infrastruttura di clock, incluso l’uso di soluzioni di clock di qualità superiore, aiuta a mitigare questi effetti. Un altro possibile metodo è filtrare digitalmente i dati con un filtro di reiezione di banda di ordine elevato a questa frequenza di offset, sebbene se implementato in modo errato, qualsiasi segnale desiderato verrà rimosso insieme alla spuria.

Un’altra sfida da superare è la correzione delle spurie di distorsione di intermodulazione del terzo ordine strettamente modulate. Queste spurie rientreranno quasi sempre nella banda passante e spesso rappresentano la spuria che limita la gamma dinamica priva di spurie. Nel caso di un fattore di decimazione molto elevato, è possibile che questi toni rientrino nella banda di attenuazione. È tuttavia improbabile che ciò si verifichi nella maggior parte dei sistemi multitono, che richiedono intrinsecamente una larghezza di banda istantanea maggiore rispetto ai sistemi monotono e quindi non possono incorporare un filtro di decimazione così ampio.

Infine, è necessario trovare il compromesso tra larghezza di banda e gamma dinamica. Sebbene la decimazione possa sopprimere componenti spurie e armoniche, comporta una riduzione della larghezza di banda istantanea. Trovare il giusto compromesso è essenziale per ottenere le migliori prestazioni per i requisiti applicativi specifici.

Vantaggi di una corretta pianificazione della frequenza mediante decimazione

Un’efficace pianificazione delle frequenze offre diversi vantaggi per migliorare la progettazione del sistema ricevitore. Uno di questi è la migliore soppressione delle spurie. I filtri di decimazione digitale attenuano efficacemente le spurie, raggiungendo spesso livelli di soppressione intorno a -85 dBFS, il che si traduce in prestazioni del segnale più pulite e in un migliore utilizzo della gamma dinamica dell’ADC per il segnale desiderato, anziché per il rumore spurio fuori banda.

Un altro vantaggio è la riduzione del throughput dei dati dall’ADC. Riducendo la velocità di trasmissione dei dati in uscita dell’ADC tramite decimazione, è possibile interfacciare l’ADC con FPGA più veloci, più piccoli e più economici. Questa riduzione dei dati trasmessi non solo semplifica i requisiti hardware, ma consente anche ai sistemi di operare in dual band o quad band, rendendo possibile così il campionamento di più bande RF contemporaneamente.

La possibilità di riconfigurare completamente un sistema tramite software è un altro vantaggio significativo dell’utilizzo della decimazione sugli ADC. È possibile pianificare l’interfaccia hardware tra l’ADC e l’FPGA in modo da supportare la massima velocità di trasmissione dati prevista dal sistema, il che faciliterebbe la possibilità di utilizzare molti altri sistemi a velocità di trasmissione dati inferiori o con larghezze di banda più ridotte. I sistemi riconfigurabili tramite software sono particolarmente preziosi nelle applicazioni che richiedono l’implementazione in più scenari.

Anche il risparmio di risorse è un risultato notevole di un’efficace pianificazione delle frequenze. Richiedendo meno corsie di uscita, siano esse corsie dati seriali ad alta velocità o coppie di segnalazione differenziale a bassa tensione, è possibile risparmiare pin preziosi sia sull’ADC che sull’FPGA, aumentando il fattore di utilizzo. Ciò è particolarmente importante nei sistemi ad alto canale con vincoli di spazio sul circuito stampato e di potenza.

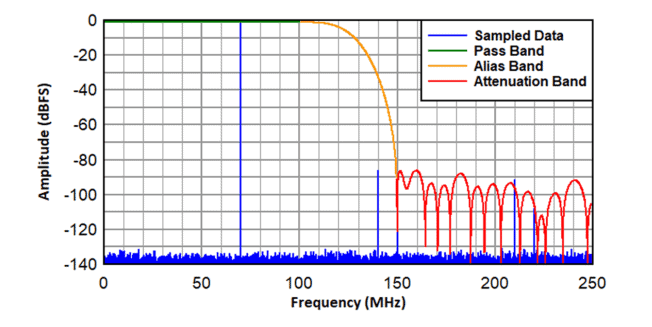

Esempio teorico: pianificazione della frequenza con decimazione

Si consideri un convertitore ADC interlacciato che campiona un comune segnale RF in ingresso a Fs. Il processo di interlacciamento introduce una spuria a Fs/2-Fin, che può interferire con il segnale desiderato. L’applicazione di un filtro di decimazione per 2, come mostrato in Figura 4, consente di attenuare questa spuria a livelli entro i limiti di reiezione del filtro di decimazione. Inoltre, il processo di decimazione riduce la velocità di trasmissione dati in uscita del convertitore ADC, consentendo un’interfaccia FPGA economica e semplificando l’elaborazione a valle. Infine, la riduzione del rumore a banda larga introduce un guadagno di processo di 3 dB, dovuto al dimezzamento del valore N (rumore) nell’SNR, mentre il valore S (segnale) rimane invariato.

Figura 4. Risposta del filtro di decimazione dei dati teorici a 500 MSPS con FIN a 70 MHz (con fattore di decimazione pari a 2).

Esempi reali: pianificazione della frequenza con decimazione

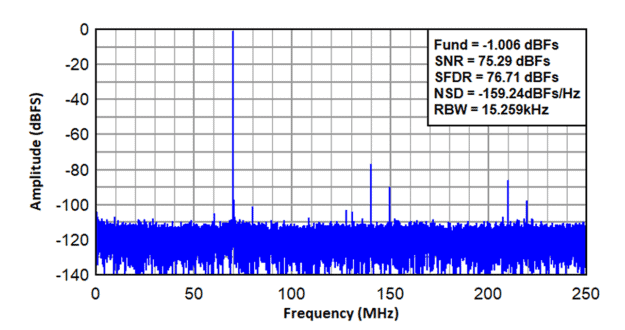

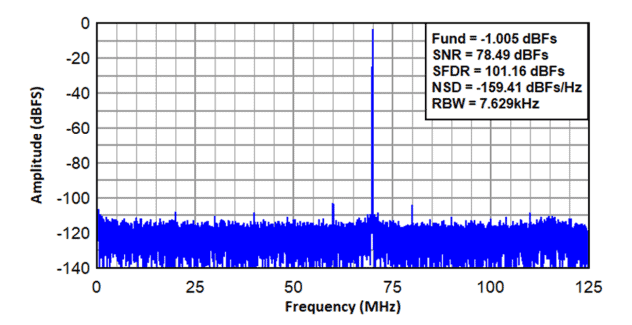

L’uso della decimazione su un ADC semplifica il processo di pianificazione delle frequenze poiché la riduzione della frequenza di campionamento riduce efficacemente la larghezza di banda di interesse. Si può pensare alla decimazione come a una focalizzazione selettiva su una parte più ristretta dello spettro. Concentrandosi su una banda più stretta, una maggiore quantità di armoniche o spurie indesiderate finisce per cadere al di fuori della banda passante di interesse e, a sua volta, viene filtrata. Gli esempi seguenti utilizzano l’ADC3669 per dimostrare la differenza che la decimazione apporta nella pianificazione delle frequenze. La Figura 5 mostra un’acquisizione di spettro tradizionale quando l’ADC non esegue la decimazione utilizzando una dimensione FFT di 16384 punti. Si può notare che le armoniche indesiderate sono in banda e influiscono negativamente sulle prestazioni.

Figura 5. Spettro reale catturato dall’ADC3669 a 500 MSPS con FIN vicino a 70 MHz (nessuna decimazione).

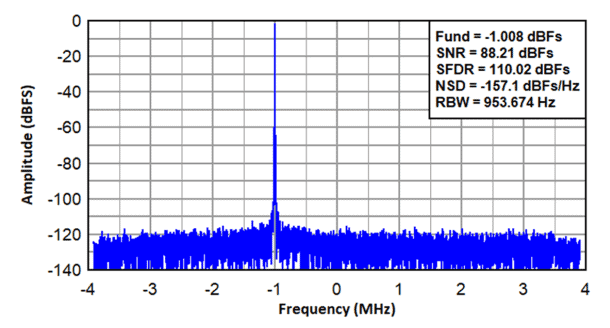

Potrebbe essere che queste armoniche siano rumore additivo generato dall’ADC o da alcune frequenze analogiche esterne. La Figura 6 mostra un esempio in cui l’ADC è in modalità di decimazione reale, con un fattore di decimazione pari a 2.

Si può notare che le armoniche spurie indesiderate ora escono dalla banda e vengono filtrate dal filtro di decimazione. Si noti che si ottiene un ulteriore miglioramento di +3 dB dovuto al guadagno di processo.

Figura 6. Spettro reale catturato dall’ADC3669 a 500 MSPS con FIN vicino a 70 MHz (con fattore di decimazione di 2).

Inoltre, la larghezza di banda di risoluzione della FFT si riduce di fatto di un fattore due, poiché manteniamo lo stesso numero di punti per il calcolo della FFT. Questo aiuta a risolvere le frequenze analogiche in intervalli più ravvicinati. Finora abbiamo parlato solo di decimazione reale, che filtra semplicemente i dati senza alcuna variazione di frequenza. La decimazione reale è ottima se il segnale di interesse cade a un valore inferiore a Fs/4 ogni volta che si decima. Ma cosa succede se si desidera decimare un segnale che cade al di fuori di questo intervallo? Il segnale di interesse spesso non è centrato sulla frequenza zero (banda base), ma piuttosto su una frequenza intermedia. È qui che entra in gioco la decimazione complessa. I convertitori-analogici (ADC) con funzionalità digitali più recenti, come l’ADC3669, incorporano un mixer NCO nello stadio DDC complesso. Miscelando il segnale di interesse con una frequenza NCO, il segnale viene spostato in banda base prima della decimazione, consentendo di sfruttare i vantaggi della decimazione per un segnale in qualsiasi punto della larghezza di banda del dispositivo.

La Figura 7 mostra un’acquisizione dell’ADC3669 in modalità di decimazione complessa con un fattore di decimazione pari a 64, che si traduce in una larghezza di banda di campionamento effettiva di 7,8125 MHz quando la FFT viene calcolata utilizzando 8192 punti. La frequenza di ingresso è 70 MHz e la frequenza NCO è 71 MHz. Quando il segnale viene miscelato con la frequenza NCO, il segnale si sposta in banda base, producendo un tono a circa -1 MHz.

Figura 7. Spettro complesso catturato dall’ADC3669 a 500 MSPS con fattore di decimazione di 64 (FIN=70 MHz, Fnco=71 MHz).

Figura 7. Spettro complesso catturato dall’ADC3669 a 500 MSPS con fattore di decimazione di 64 (FIN=70 MHz, Fnco=71 MHz).

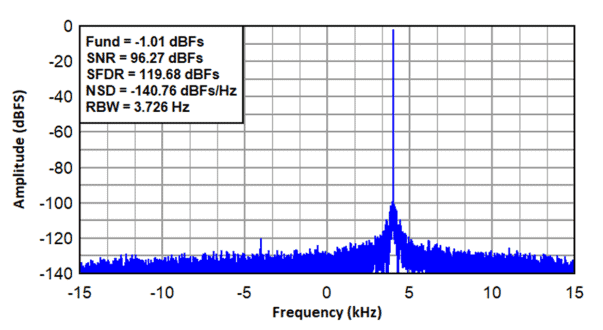

L’ADC3669 può catturare una banda stretta con un fattore di decimazione fino a 32768, il che è vantaggioso per applicazioni con bande RF ad alta densità o spaziatura tra i canali ridotta. Una decimazione con un fattore così elevato consente di ingrandire il segnale di interesse, filtrando praticamente tutto il resto. La gamma di fattori di decimazione offerti dai moderni ADC come l’ADC3669 consente una maggiore flessibilità nella pianificazione delle frequenze, poiché è molto più facile filtrare le spurie indesiderate. La Figura 8 mostra un’acquisizione con un fattore di decimazione di 16384 calcolato utilizzando 8192 punti FFT, con una larghezza di banda di risoluzione di 3,726 Hz. Anche se le spurie si trovano entro migliaia di hertz dalla fondamentale, è possibile filtrarle facilmente con un elevato tasso di decimazione.

Figura 8. Spettro complesso catturato dall’ADC3669 a 500 MSPS con fattore di decimazione di 16384 (FIN=70 MHz, Fnco=69,996 MHz).

Poiché la frequenza NCO è inferiore di 4 kHz rispetto al segnale di ingresso, il segnale convertito in basso appare con un offset di frequenza positivo. Operando in questa modalità di decimazione e a 500 MSPS, questo ADC può campionare segnali entro un intervallo di 30,517 kHz attorno alla frequenza NCO programmabile.

Conclusione

La pianificazione delle frequenze è un aspetto essenziale della progettazione di sistemi basati su ADC, che affronta sfide come la gestione delle spurie, l’ottimizzazione della gamma dinamica e la progettazione di AAF, nonché l’efficiente gestione dei dati. Implementando un’attenta pianificazione delle frequenze in anticipo, è possibile evitare insidie comuni come le sovrapposizioni delle zone di Nyquist e la contaminazione delle spurie di clock, beneficiando al contempo di vantaggi quali una migliore soppressione delle spurie e una gamma dinamica migliorata, una riduzione dell’interfaccia digitale o della velocità di trasmissione dati dell’ADC e un risparmio di risorse FPGA. Un attento bilanciamento di questi compromessi e l’utilizzo di funzionalità come la decimazione dell’ADC consentono di ottenere sistemi di ricezione ad alte prestazioni e riconfigurabili tramite software per una vasta gamma di applicazioni, evitando al contempo il successivo buco di campionamento.

Siti web correlati

- Scopri le tecniche per il salto di frequenza rapido nei convertitori di dati di campionamento RF consultando SLYT861: Exploring fast frequency hopping in RF sampling data converters di Chase Wood, pubblicato sull’Analog Design Journal, ottobre 2024.

- Comprendere la relazione tra campionamento e velocità dei dati con TIPL4701: Campionamento vs. velocità dei dati, decimazione (DDC) e interpolazione (DUC) nei convertitori di dati ad alta velocità di Jim Seton, pubblicato nell’agosto 2017.

- Per approfondimenti su esempi di decimazione a larghezza di banda più elevata, leggi Analyzing High-Bandwidth Spectrum Clusters di Chase Wood, pubblicato su Embedded Computing Design, maggio 2024.

- Ottimizza la pianificazione della frequenza di campionamento RF utilizzando il pianificatore di frequenza di campionamento RF, il filtro analogico e il calcolatore DDC. Per specifiche dettagliate, consulta la scheda tecnica del TI ADC3669.

Luke Allen è Applications Engineer presso Texas Instruments, Rob Reeder è High-Speed Converter Application Engineer presso Texas Instruments e Chase Wood è Applications Engineer presso Texas Instruments.