Il passaggio a 3 nm consente di ridurre i costi e il consumo energetico, pur mantenendo l’integrità e le prestazioni del segnale, per aiutare i fornitori di servizi cloud a stare al passo con la crescente domanda di maggiore velocità e maggiore capacità di trasferimento dati.

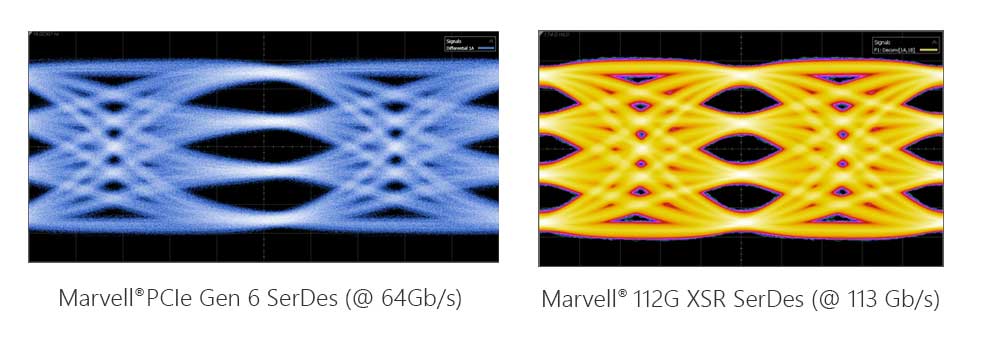

Marvell Technology ha dimostrato le interconnessioni in silicio ad alta velocità e larghezza di banda ultraelevata prodotte presso la TSMC con nodo di processo a 3 nm. I primi elementi costitutivi in silicio di Marvell con questo nodo includono 112G XSR SerDes (serializzatore / deserializzatore), Long Reach SerDes, PCIe Gen 6 / CXL 3.0 SerDes e un’interconnessione parallela die-to-die da 240 Tbps.

I nuovi elementi costitutivi fanno parte della strategia di Marvell volta a sviluppare un portafoglio completo di IP in silicio per la progettazione di chip che aumenteranno radicalmente la larghezza di banda, le prestazioni e l’efficienza energetica dell’infrastruttura dati di prossima generazione. Queste tecnologie supportano anche tutte le opzioni di packaging dei semiconduttori, dagli RDL (Redistribution Layers) standard e a basso costo all’interconnessione ad alta densità basata su silicio.

Marvell è stato il primo fornitore di silicio per infrastrutture dati a campionare e rilasciare rispettivamente in commercio i SerDes 112G leader del settore ed è stato leader nei prodotti per infrastrutture di dati basati sul processo a 5 nm di TSMC.

SerDes e interconnessioni parallele fungono da percorsi ad alta velocità per lo scambio di dati tra chip o componenti in silicio all’interno dei chiplet. Insieme al packaging 2.5D e 3D, queste tecnologie consentono di eliminare i colli di bottiglia a livello di sistema per far progredire i progetti di semiconduttori più complessi. SerDes aiuta anche a ridurre i pin, le tracce e lo spazio sulla scheda del circuito per ridurre i costi. Un rack in un data center hyperscale può contenere decine di migliaia di collegamenti SerDes.

La nuova interconnessione parallela die-to-die, ad esempio, consente trasferimenti di dati aggregati fino a 240 Tbps, il 45% più veloce rispetto alle alternative disponibili per le applicazioni di packaging multichip.

Marvell incorpora i suoi SerDes e le tecnologie di interconnessione nelle sue soluzioni di silicio di punta, tra cui switch Teralynx, PAM4 e DSP coerenti, dispositivi PHY (Physical Layer) Ethernet Alaska, processori OCTEON, controller di storage Bravera, chipset Ethernet automobilistici Brightlane e ASIC personalizzati. Il passaggio a un processo a 3 nm consente agli ingegneri di ridurre i costi e il consumo energetico dei chip e dei sistemi di elaborazione, mantenendo l’integrità e le prestazioni del segnale.

“Le interconnessioni stanno assumendo un’importanza sempre maggiore man mano che i cloud e altri sistemi informatici crescono in dimensioni, complessità e capacità. Le nostre interfacce SerDes e parallele avanzate svolgeranno un ruolo significativo nel fornire una piattaforma per lo sviluppo di chip con larghezza di banda, latenza, tasso di errore di bit ed efficienza energetica migliori della categoria per soddisfare le esigenze dell’IA e altri carichi di lavoro complessi“, ha affermato Raghib Hussain, president of products and technologies at Marvell. “Siamo orgogliosi di poter offrire tali progressi sulla tecnologia a 3 nm di TSMC e portare i progetti di semiconduttori a un livello superiore per i nostri clienti in tutto il mondo“.

“La larghezza di banda è la linfa vitale del cloud. I fornitori di servizi stanno aumentando la loro capacità di rete di circa il 50% all’anno nel cloud e di oltre il 100% per le applicazioni AI“, ha affermato Alan Weckel, co-fondatore di 650 Group. “La produzione Marvell di SerDes e interconnessioni a 3 nm segna l’ultimo passo per aiutare i fornitori di servizi cloud a stare al passo con la domanda sempre crescente di velocità più elevate e più traffico“.

“Ci congratuliamo con Marvell per il raggiungimento di questa importante pietra miliare nello sviluppo del silicio nella tecnologia di processo a 3 nm all’avanguardia del settore“, ha affermato Joachim Peerlings, general manager of Keysight’s Communications Solutions Group. “Siamo molto soddisfatti dei nostri progressi sulla più ampia abilitazione del settore ed entusiasti di lavorare con i migliori innovatori tecnologici come Marvell per mostrare le tecnologie di interconnessione di prossima generazione che aiuteranno a spingere i confini della progettazione, delle prestazioni e dell’efficienza energetica dell’infrastruttura di dati in silicio“.